## **SR2500**

## VXI Digital Test Subsystem

**Includes Coverage of:**

- o SR2500 Subsystem

- o SR2510 Main Module

- o SR2520 Expansion Module

- o SR2520 w/Guided Probe Option

- o RG2500 Rail Generator

- o WaveEdit Digital Waveform Editor

Rev. 05 Jun. '98

## **\*Proprietary Notice\***

This document, and the technical information contained herein, are proprietary of Interface Technology and shall not, without the express written permission of Interface Technology, be used in any form or part to solicit competitive quotations. The information provided herein may be used for operational purposes only, or for the purpose of incorporation into technical specifications or other documents which specify procurement from Interface Technology.

## **\*DISCLAIMERS**\*

Interface Technology, Inc. makes no warranty of any kind with regard to this material, including, but not limited to, implied warranties or fitness for a particular use or purpose.

Interface Technology, Inc. shall not be liable for errors contained herein or for incidental or consequential damages in connection with the performance or use of this material.

Interface Technology, Inc. reserves the right to make changes to its products and to the content of this manual without notice.

## **User's Manual**

# SR2500 System Overview and Programmer's Guide

Rev. 05 Apr 1998 Change 2 Oct 2000

## Contents

| Chapter 1                   | About This Manual                            |      |

|-----------------------------|----------------------------------------------|------|

| General Description         | Arrangement of Manual                        |      |

|                             | Arrangement of Contents, This Manual         |      |

|                             | Applicability                                |      |

|                             | Supersedure Notice                           |      |

|                             | Equipment Description                        |      |

|                             | SR2510 Main Module                           |      |

|                             | SR2520 Expansion Module                      |      |

|                             | SR2520 w/Guided Probe (option)               |      |

|                             | RG2500 Rail Generator (option)               |      |

| Chapter 2                   | Test Programs                                | 2-1  |

| Test Programming Parameters | Fields                                       |      |

| 5 5                         | Non-Algorithmic Fields                       |      |

|                             | Algorithmic Fields                           |      |

|                             | Hardware Fields                              |      |

|                             | Vector Looping                               |      |

|                             | Program Branching                            |      |

|                             | GOTO                                         |      |

|                             | GOSUB                                        |      |

|                             | RETURN                                       |      |

|                             | Data Rates                                   |      |

|                             | VME A32 Dual Access Memory                   |      |

|                             | Output Data Formatiing                       |      |

|                             | NRZ (Non-Return-to-Zero)                     |      |

|                             | RZ (Return-to-Zero)                          |      |

|                             | RONE (Return-to-One)                         |      |

|                             | RC (Return-to-Compliment)                    |      |

|                             | RI (Return-to-Inhibit/Tristate)              |      |

|                             | Input Data Formatting                        |      |

|                             | Edge Mode                                    |      |

|                             | Window Mode                                  |      |

|                             | Memory                                       |      |

|                             | Control Memory                               |      |

|                             | Stimulus Memory                              |      |

|                             | Output Memory                                |      |

|                             | Tristate Memory                              |      |

|                             | Stimulus Algorithmic Memory                  |      |

|                             | Response Memory                              |      |

|                             | Record Memory                                |      |

|                             | Record Memory and Signature Analysis Control |      |

|                             | Programming Languages                        | 2-10 |

| Chapter 3   | SCPI Command Syntax                          |      |

|-------------|----------------------------------------------|------|

| Programming | Basic Programming                            |      |

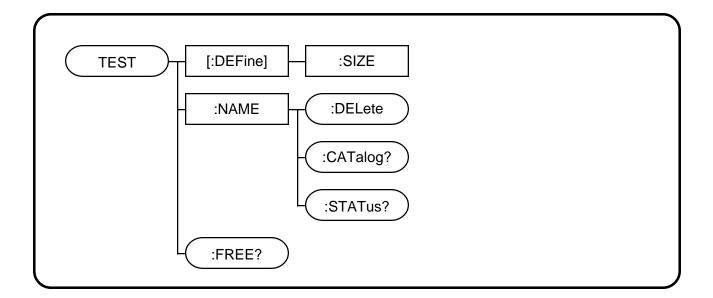

|             | Defining Tests                               |      |

|             | Test Definition                              |      |

|             | Test Deletion                                |      |

|             | Test Definition Catalog                      |      |

|             | Test Definition Status Query                 |      |

|             | Free Vector Space Query                      | 3-10 |

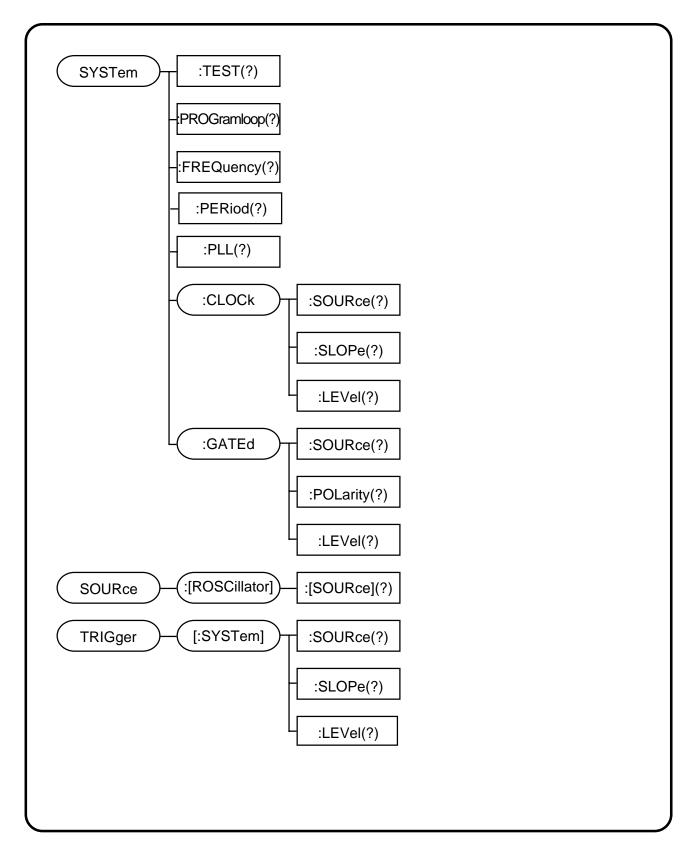

|             | Global Test Parameters                       |      |

|             | Selecting the Active Test                    |      |

|             | Setting the Program Loop Count               |      |

|             | Setting the Test System Frequency            |      |

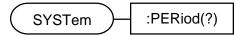

|             | Setting the Test System Period               |      |

|             | Setting the System Clock Frequency           | 3-18 |

|             | Selecting the System Clock Source            |      |

|             | Selecting the Slope of the External Clock    |      |

|             | Setting the External Clock Threshold Level   |      |

|             | Selecting the System Gate Source             |      |

|             | Setting the External Gate Threshold Level    |      |

|             | Selecting the Polarity of the External Gate  |      |

|             | Selecting the Reference Oscillator Source    |      |

|             | Selecting the System Trigger Source          |      |

|             | Selecting the Slope of the External Trigger  |      |

|             | Setting the External Trigger Threshold Level |      |

|             | Field Definitions                            |      |

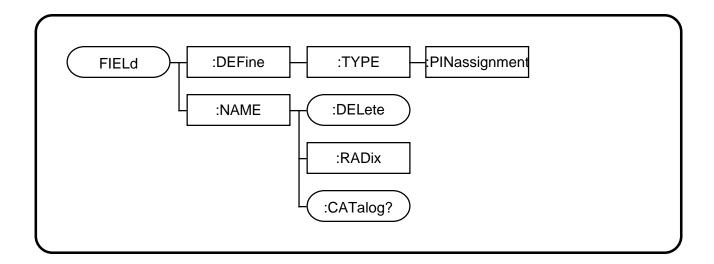

|             | Field Definition & Pin Assignment            |      |

|             | Field Deletion                               |      |

|             | Selecting the Field Radix                    |      |

|             | Field Definition Catalog                     |      |

|             | Loading and Querying Test Vectors            |      |

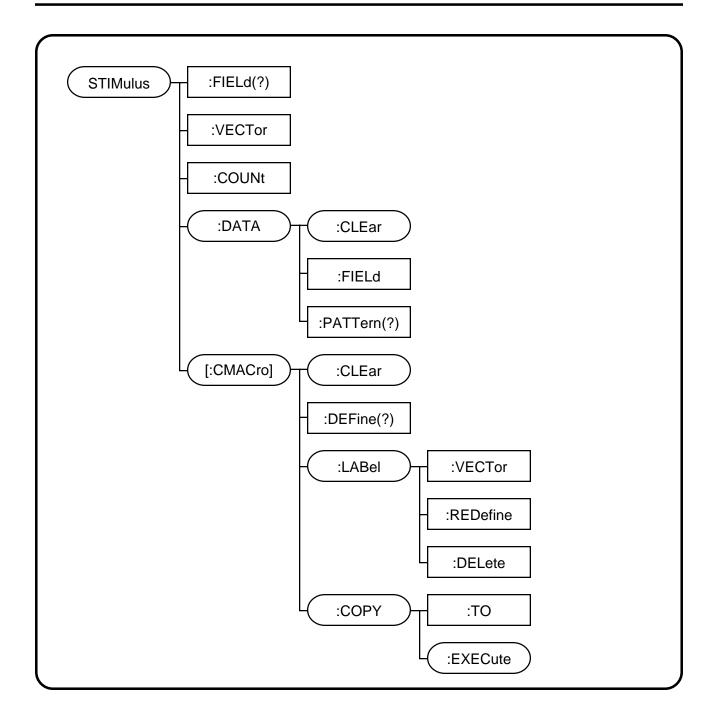

|             | Selecting the Default Stimulus Field         |      |

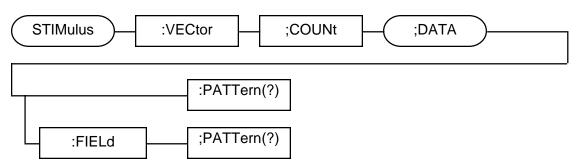

|             | Loading/Querying Stimulus Patterns           |      |

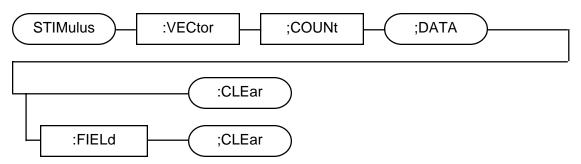

|             | Clearing Stimulus Patterns                   |      |

|             | Enabling the Armdata Function                |      |

|             | Setting the Armdata Pattern                  |      |

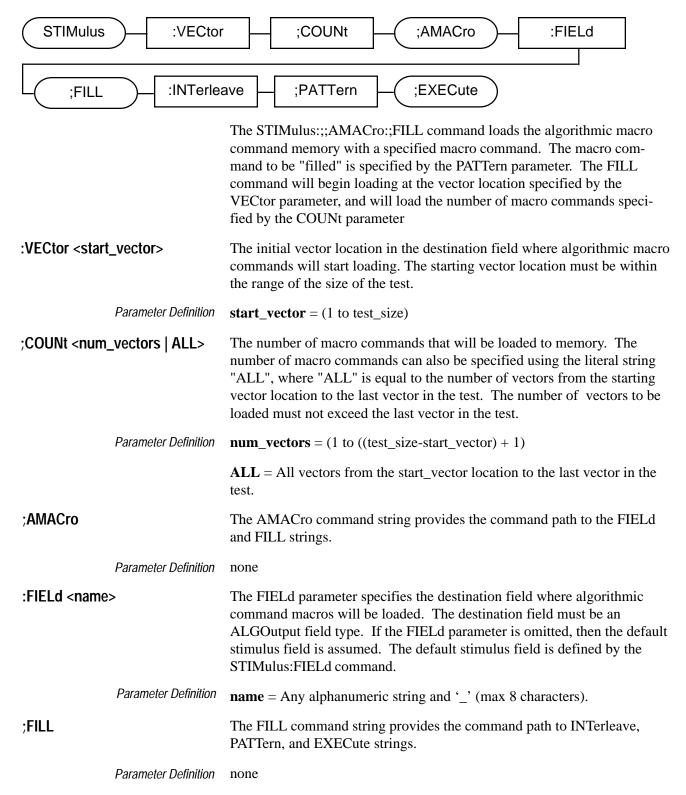

|             | Loading the Stimulus Macro Command Memory    |      |

|             | COMMAND DEFINITIONS                          |      |

|             | SProgram[(OUT)]                              | 3-58 |

|             | EProgram[(OUT)]                              |      |

|             | OUTput[(OUT)]                                |      |

|             | WLoopuntil([OUT]( <loop_cond>))</loop_cond>  |      |

| SLoopuntil([OUT]( <loop_cond>))</loop_cond>          |              |

|------------------------------------------------------|--------------|

| ELoop[(OUT)]                                         |              |

| SCONDition([OUT]( <jump_cond>))</jump_cond>          |              |

| SJMPPage(Supported Only on 256K and 1M Vector Cards) |              |

| JMP([OUT]( <label_name>))</label_name>               |              |

| JSRoutine([OUT]( <label_name>))</label_name>         |              |

| RTSubroutine[(OUT]                                   |              |

| CJMP([OUT]( <label_name>))</label_name>              |              |

| CJSRoutine([OUT]( <label_name>))</label_name>        |              |

| CRTSubroutine[(OUT)]                                 |              |

| CLEARError[(OUT)]                                    | 3-64         |

| CONDITION DEFINITIONS                                | 3-64         |

| COUNt == count_value                                 | 3-64         |

| RCOMpare == TRUE                                     |              |

| RCOMpare != TRUE                                     |              |

| LATCherror == TRUE                                   |              |

| LATCherror != TRUE                                   |              |

| STRigger == TRUE                                     | 3-65         |

| FRONtpanel && match_pattern                          | 3-65         |

| FRONtpanel &!match_pattern                           |              |

| QUALifword && qual_combination                       |              |

| QUALifword &! qual_combination                       |              |

| Redefining Macro Command Label Vectors               | 3-68         |

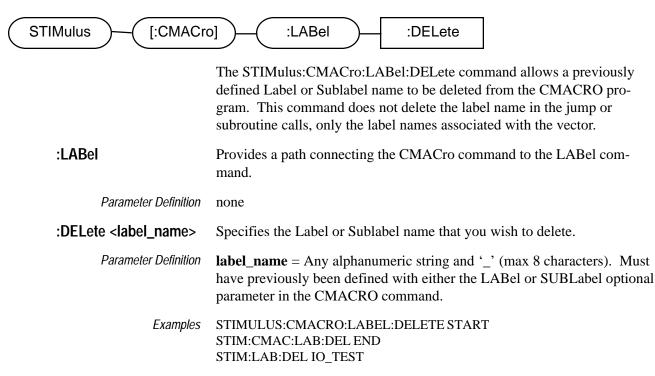

| Deleting Macro Command Labels                        | 3-69         |

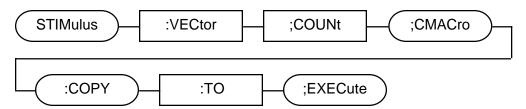

| Copying Stimulus Macro Commands                      |              |

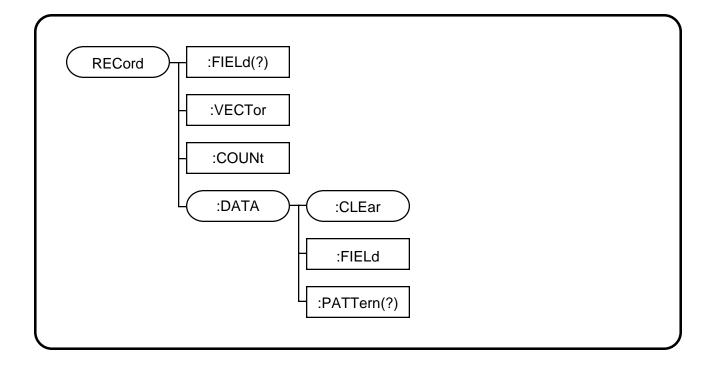

| Selecting the Default Record Field                   | 3-72         |

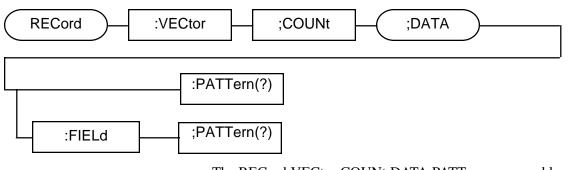

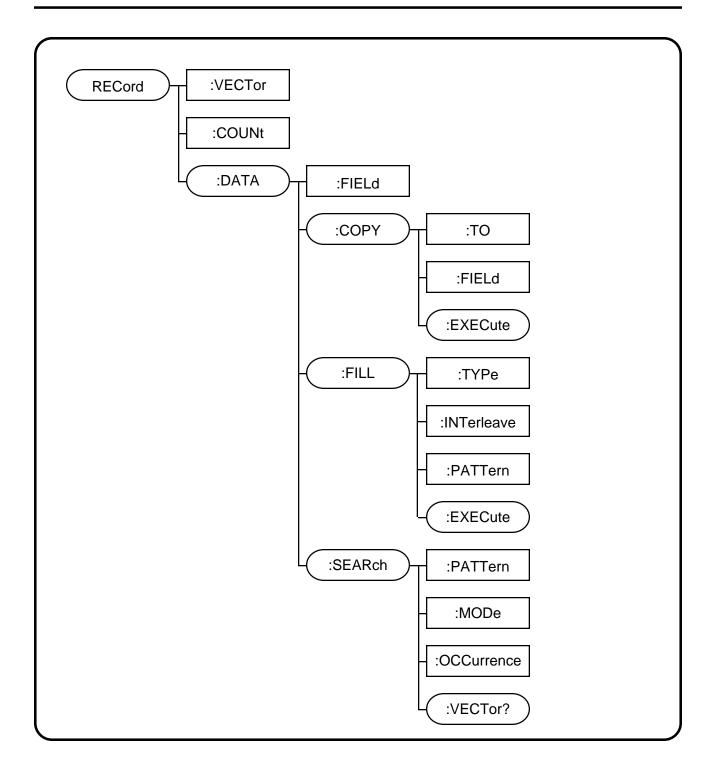

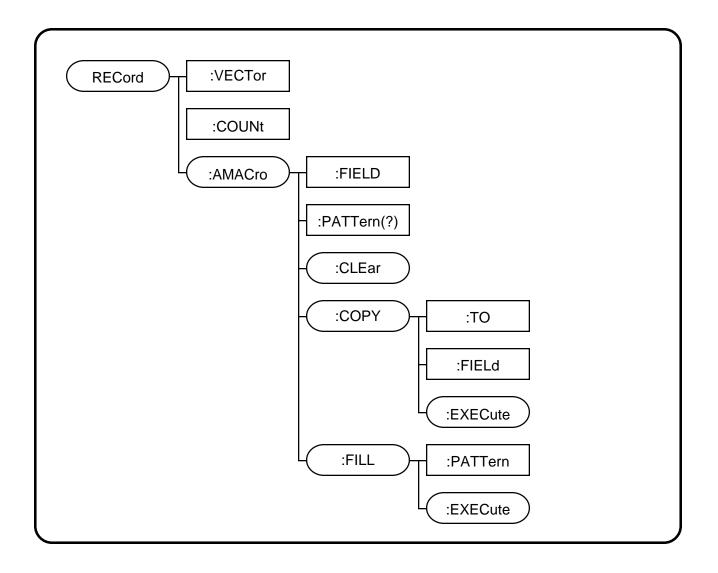

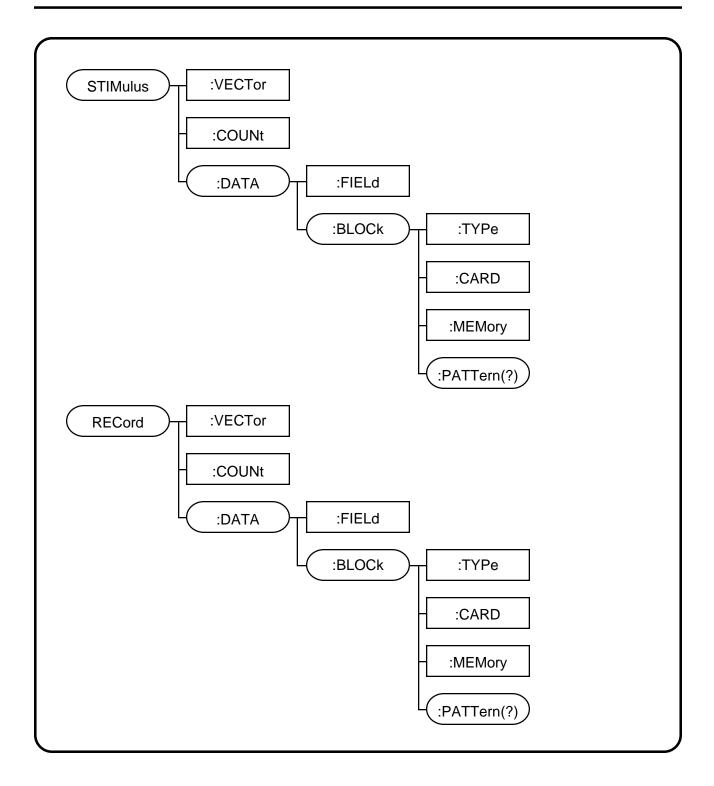

| Loading/Querying Record Patterns                     | 3-73         |

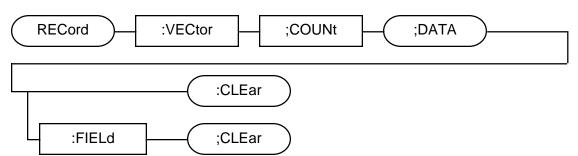

| Clearing Record Patterns                             | 3-76         |

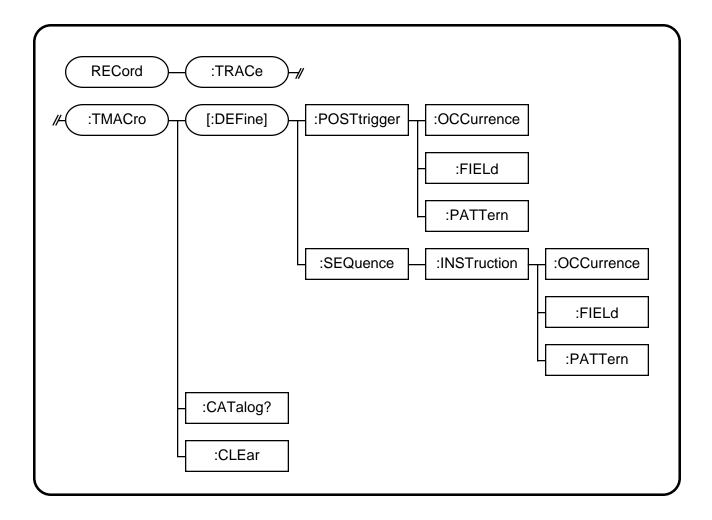

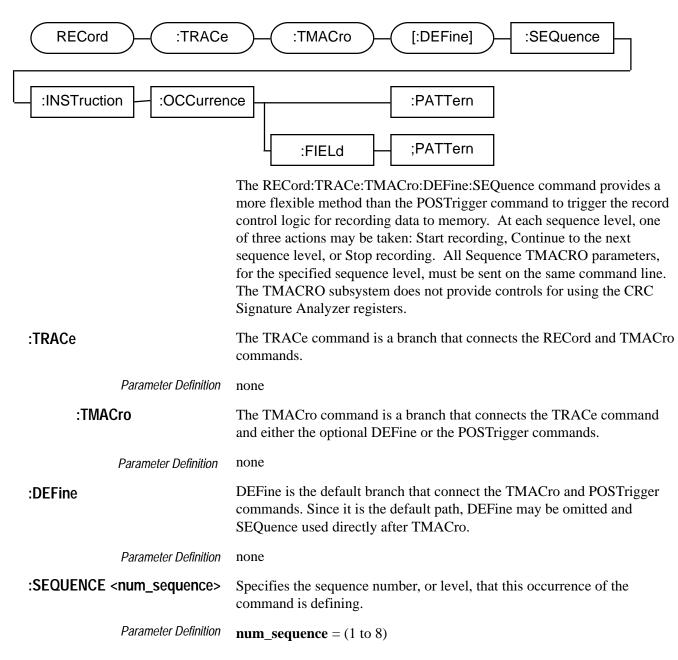

| Trace TMACRO's                                       | <b>3-7</b> 8 |

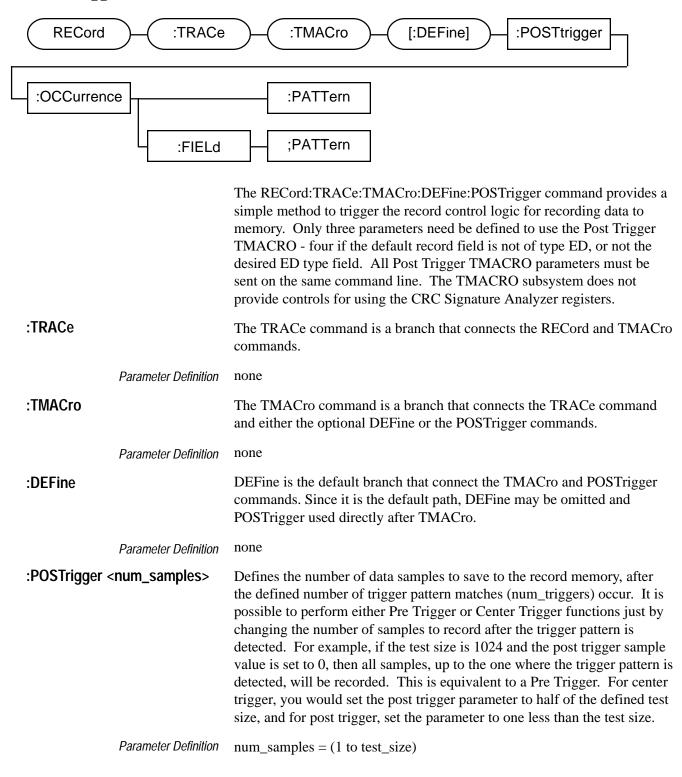

| Post Trigger TMACRO Definition                       | 3-80         |

| Sequencing TMACRO Definition                         |              |

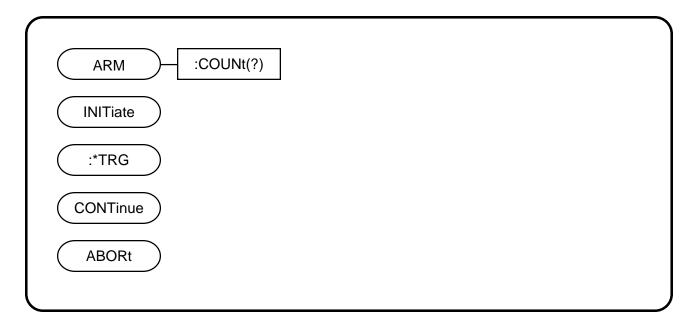

| Run Time Commands                                    | 3-87         |

| Setting the Arm Counter                              | 3-88         |

| Initializing the Test Program                        |              |

| Software Trigger Command                             |              |

| Test Program Abort Command                           |              |

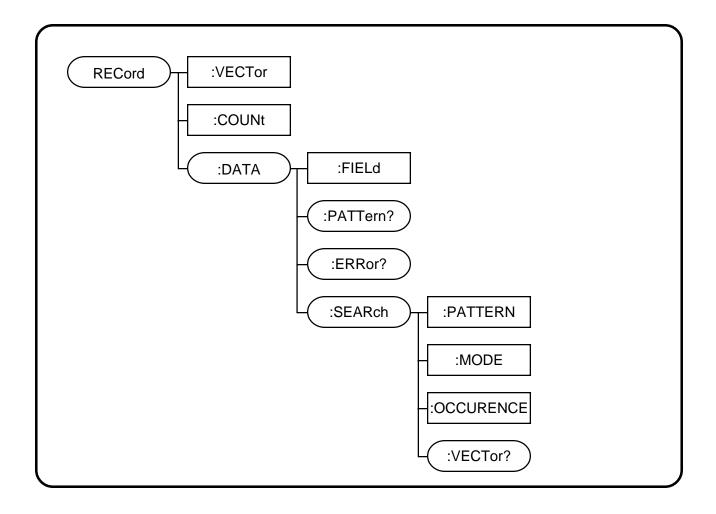

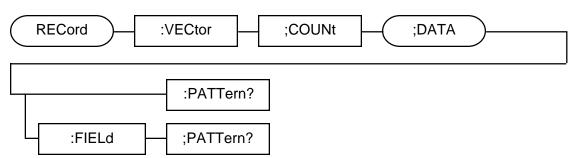

| Reading Recorded Data 3-92                   |

|----------------------------------------------|

| Reading Recorded Patterns                    |

| Compare Error Status Query                   |

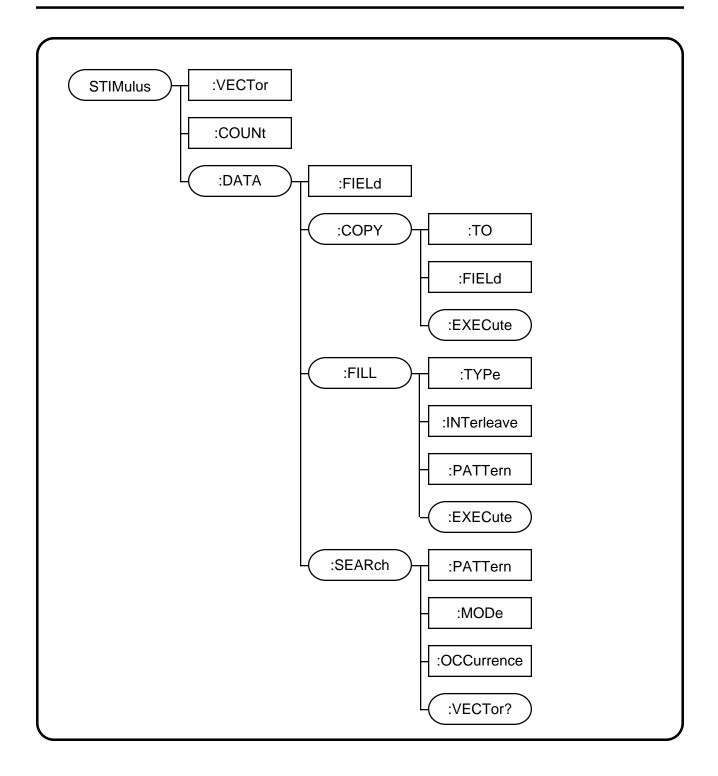

| Searching Record Memory                      |

|                                              |

| Advanced Programming 3-101                   |

| Pattern Editing 3-102                        |

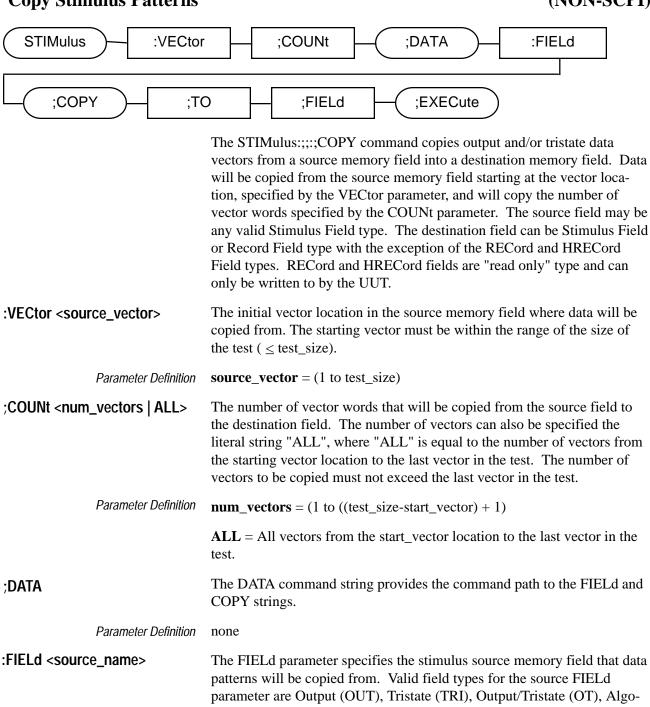

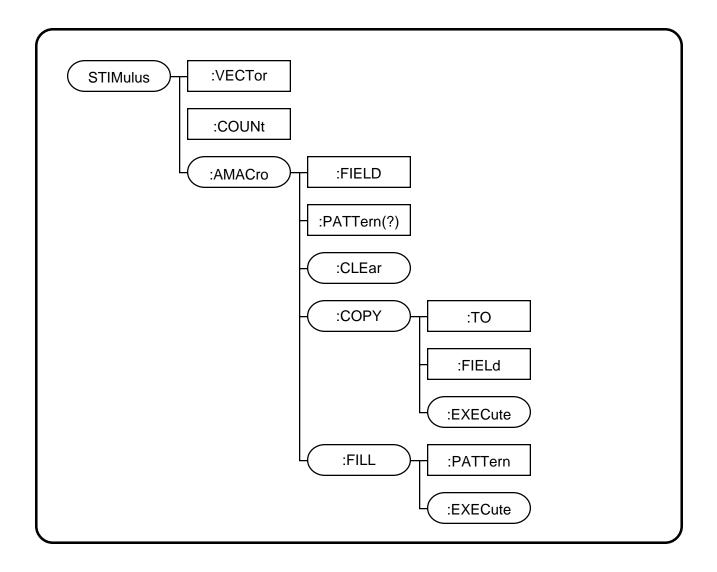

| Copy Stimulus Patterns                       |

| Filling Stimulus Memory 3-108                |

| Searching Stimulus Memory 3-112              |

| Copying Record and Response Patterns 3-115   |

| Filling Response Memory 3-118                |

| Searching Response Memory 3-122              |

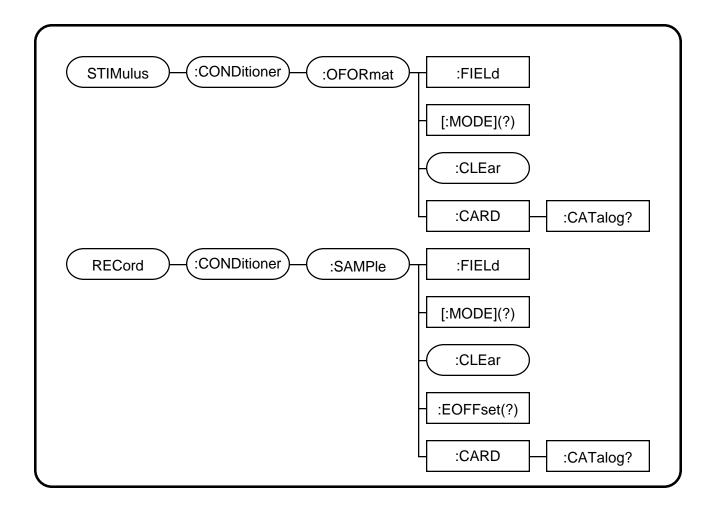

| I/O Formatting and Timing 3-126              |

| Stimulus Format and Timing 3-128             |

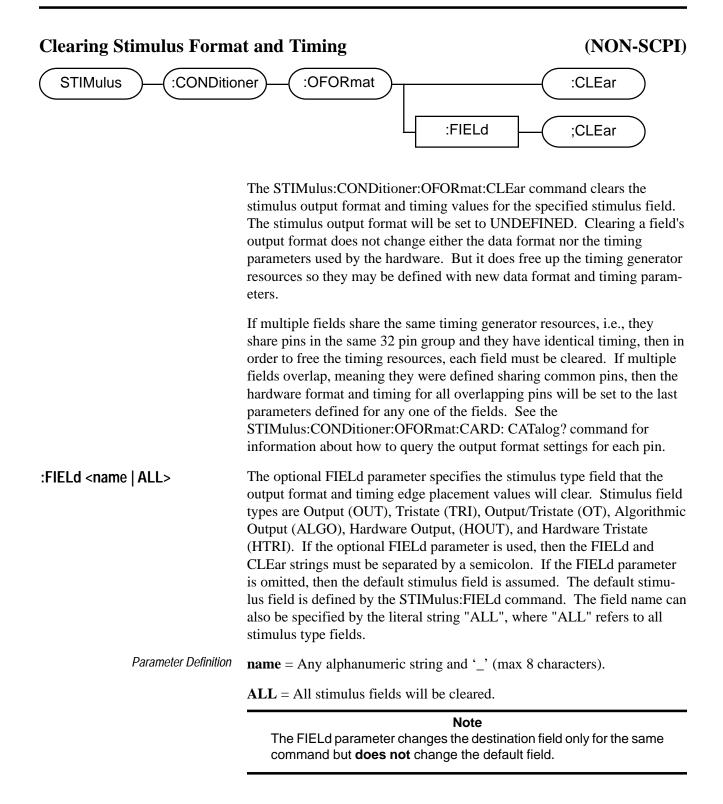

| Clearing Stimulus Format and Timing 3-131    |

| Stimulus Format and Timing Catalog           |

| Record Sample Mode and Timing                |

| Clearing Record Sample Mode and Timing 3-138 |

| Expected Compare Offset 3-140                |

| Record Sample Mode and Timing Catalog 3-141  |

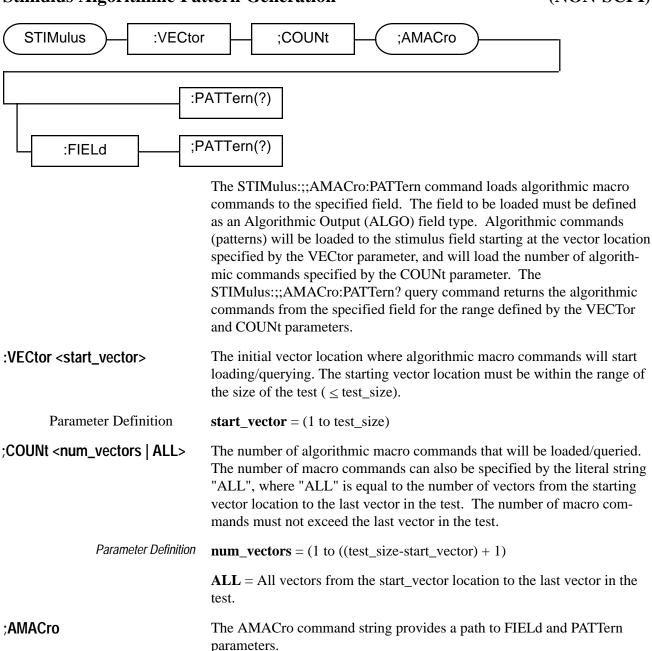

| Algorithmic Pattern Generation 3-142         |

| Stimulus Algorithmic Pattern Generation      |

| Algorithmic Output Command Definitions 3-147 |

| NONAlgorithmic                               |

| INCrement                                    |

| DECrement                                    |

| XOR                                          |

| HOLDData                                     |

| HOLDAII                                      |

| SLEFTZero                                    |

| SLEFTOne                                     |

| SLEFTComplement                              |

| RLEFT                                        |

| SRIGHTZero                                   |

| SRIGHTOne                                    |

| SRIGHTComplement                             |

| RRIGHT                                       |

| LOADProgram<br>OUTPUTParm               | 3-149 |

|-----------------------------------------|-------|

| Clearing Stimulus Algorithmic Memory    | 3-151 |

| Copying Stimulus Algorithmic Commands   | 3-153 |

| Filling Stimulus Algorithmic Memory     | 3-155 |

|                                         |       |

| Response Algorithmic Pattern Generation | 3-157 |

| Algorithmic Expect Command Definitions  | 3-159 |

| NONAlgorithmic                          |       |

| INCrement                               |       |

| DECrement                               |       |

| XOR                                     |       |

| HOLDData                                |       |

| HOLDAII                                 |       |

| SLEFTZero                               |       |

| SLEFTOne                                |       |

| SLEFTComplement                         |       |

| RLEFT                                   |       |

| SRIGHTZero                              |       |

| SRIGHTOne                               |       |

| SRIGHTComplement                        |       |

| RRIGHT                                  |       |

| LOADParam                               |       |

| OUTPUTParm                              |       |

| Clearing Response Algorithmic Memory    |       |

| Copying Response Algorithmic Commands   |       |

| Filling Response Algorithmic Memory     |       |

| Thing Response Argonunite Memory        | 5-107 |

| High Speed Binary Pattery Transfers     | 3-170 |

| Stimulus Mapped Binary Patterns         | 3-172 |

| Stimulus Non-Mapped Binary Patterns     |       |

| Record Mapped Binary Patterns           |       |

| Record Non-Mapped Binary Patterns       |       |

|                                         | 0 1/0 |

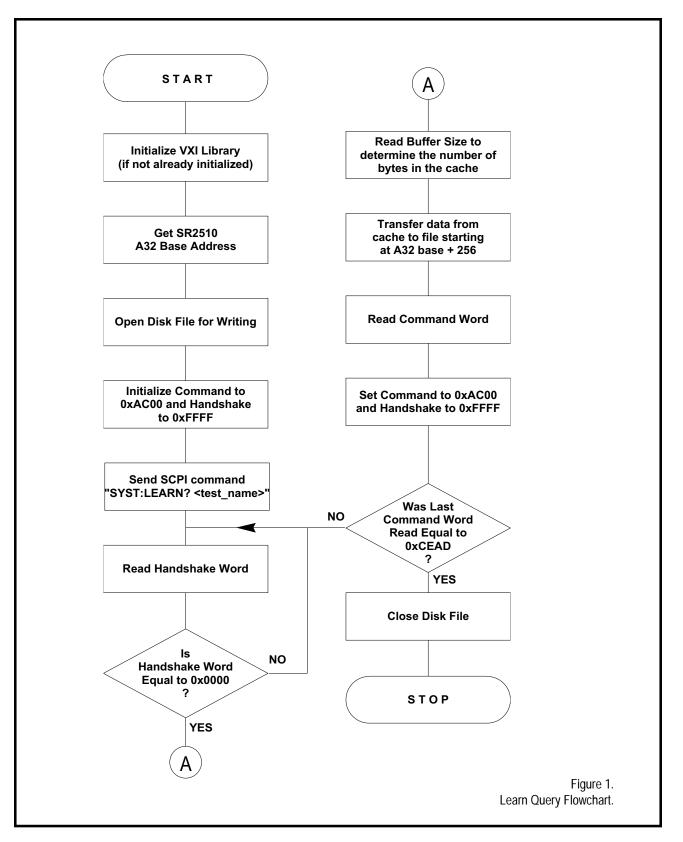

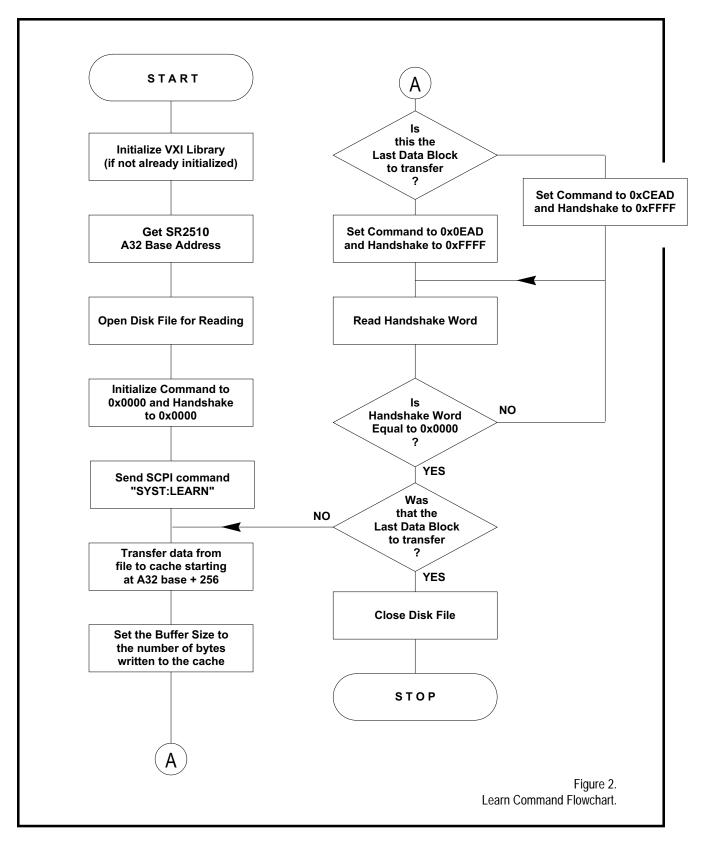

| Saving and Loading Tests                | 3-180 |

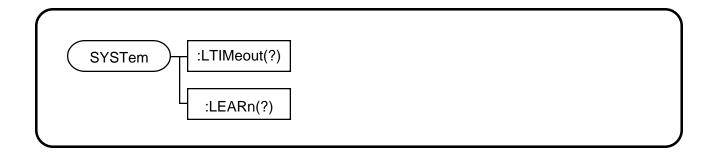

| Binary Learn Time-Out                   | 3-182 |

| Learning Binary Tests                   |       |

|                                         | 2 105 |

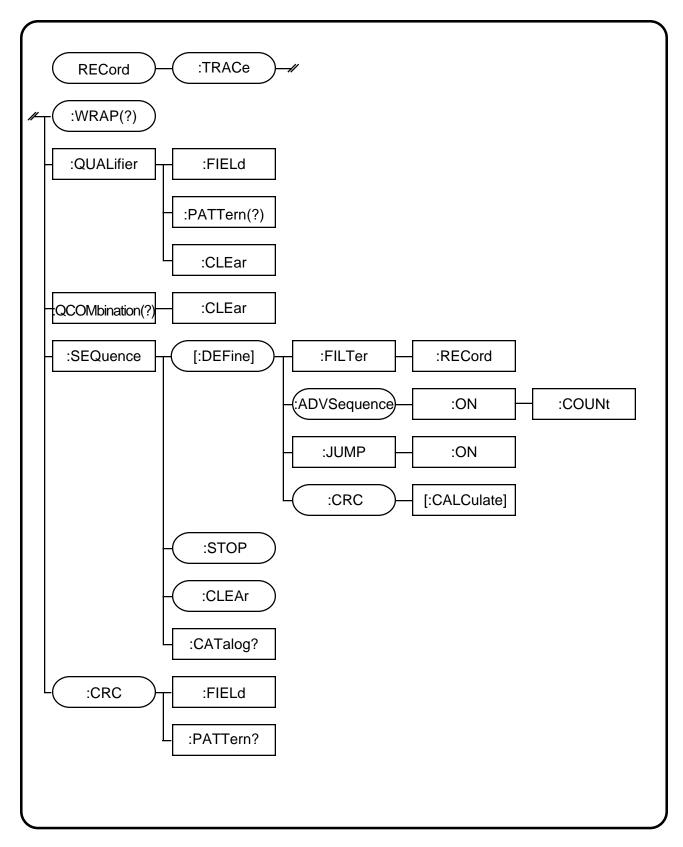

| Advanced Record Triggering              | 3-184 |

| Record Memory Wrapping                                                                                                                                                                                                                                                                                                | 3-187                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

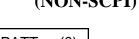

| Qualifier Trigger Patterns                                                                                                                                                                                                                                                                                            |                                                                                                                               |

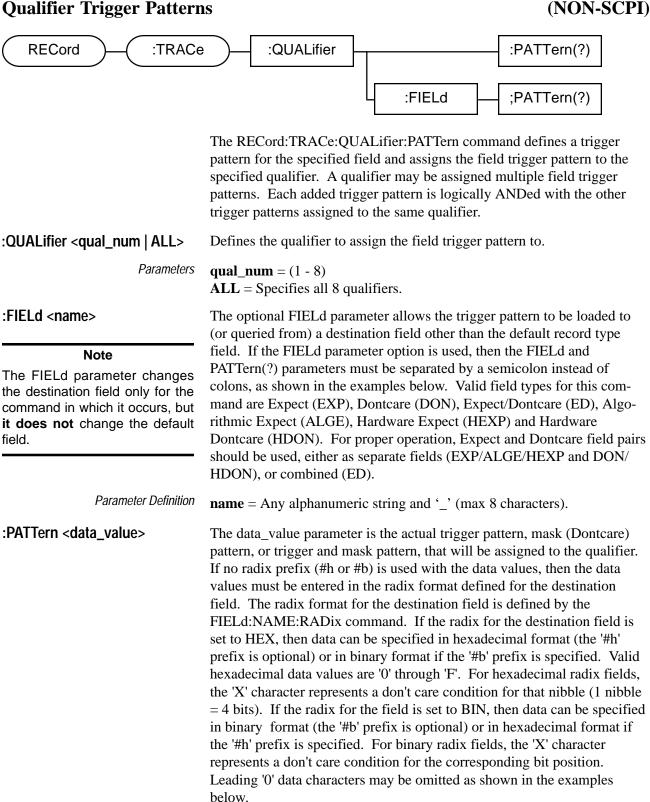

| Clearning Qualifier Trigger Patterns                                                                                                                                                                                                                                                                                  |                                                                                                                               |

| Qualifier Trigger Combinations                                                                                                                                                                                                                                                                                        |                                                                                                                               |

| Clearing Qualifier Trigger Combinations                                                                                                                                                                                                                                                                               |                                                                                                                               |

| Record Filter and Control                                                                                                                                                                                                                                                                                             | 3-193                                                                                                                         |

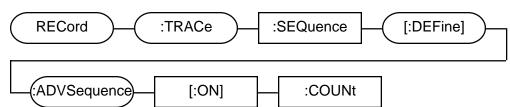

| Advancing Trace Sequences                                                                                                                                                                                                                                                                                             | 3-195                                                                                                                         |

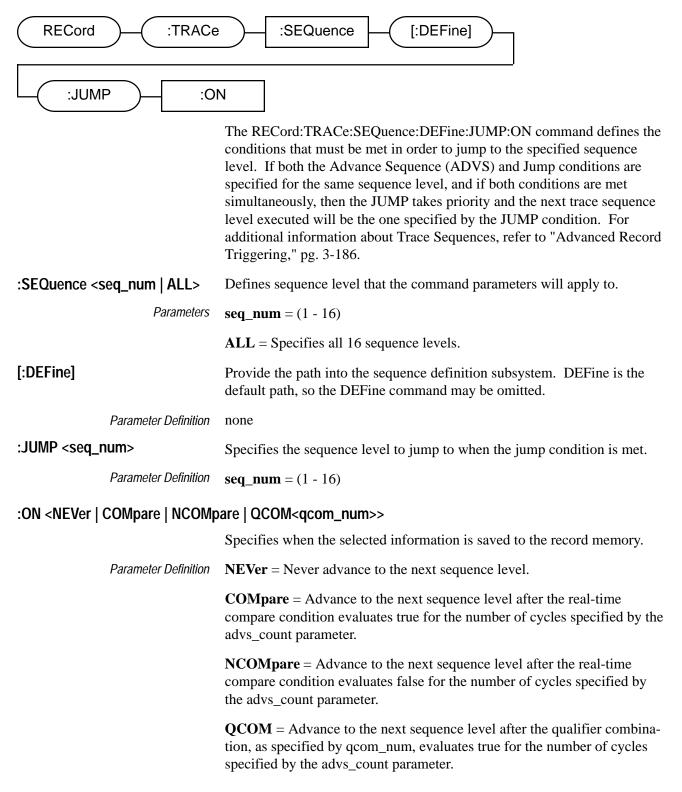

| Jumping to Trace Sequences                                                                                                                                                                                                                                                                                            | 3-197                                                                                                                         |

| CRC Calculation Control                                                                                                                                                                                                                                                                                               |                                                                                                                               |

| Stopping Tests from Trace Sequences                                                                                                                                                                                                                                                                                   | 3-201                                                                                                                         |

| Clearing Trace Sequences                                                                                                                                                                                                                                                                                              | 3-202                                                                                                                         |

| Trace Sequences Catalog                                                                                                                                                                                                                                                                                               | 3-203                                                                                                                         |

| Querying CRC Checksums                                                                                                                                                                                                                                                                                                | 3-205                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

| Miscellaneous Commands                                                                                                                                                                                                                                                                                                | 3-207                                                                                                                         |

| Discussion                                                                                                                                                                                                                                                                                                            | 2 200                                                                                                                         |

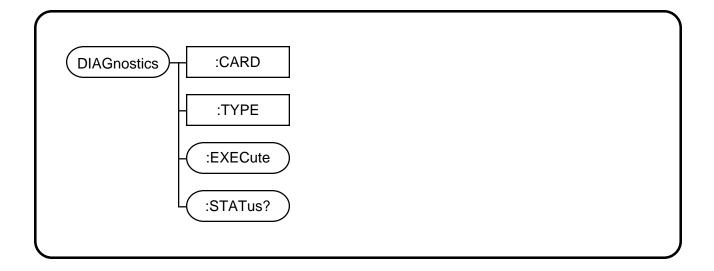

| Diagnostics                                                                                                                                                                                                                                                                                                           |                                                                                                                               |

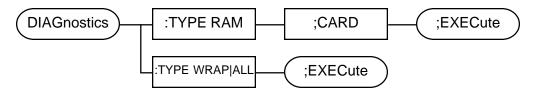

| Diagnostic Test Execution                                                                                                                                                                                                                                                                                             |                                                                                                                               |

| Diagnostic Test Status Query                                                                                                                                                                                                                                                                                          | 3-212                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

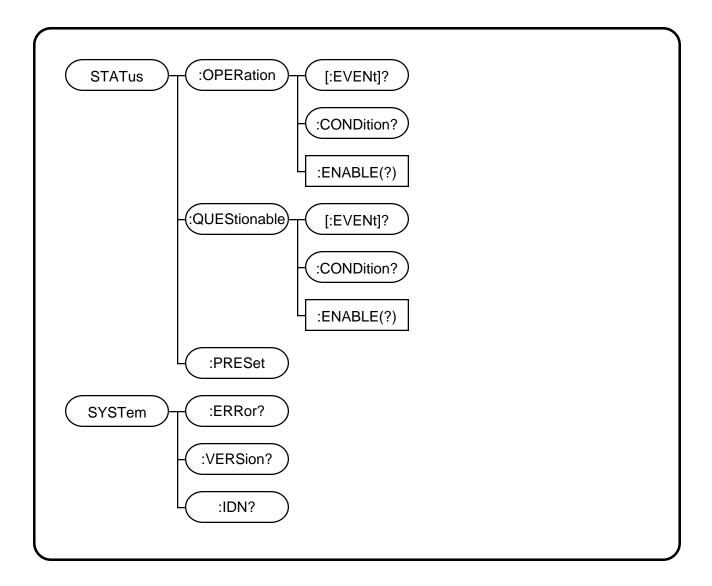

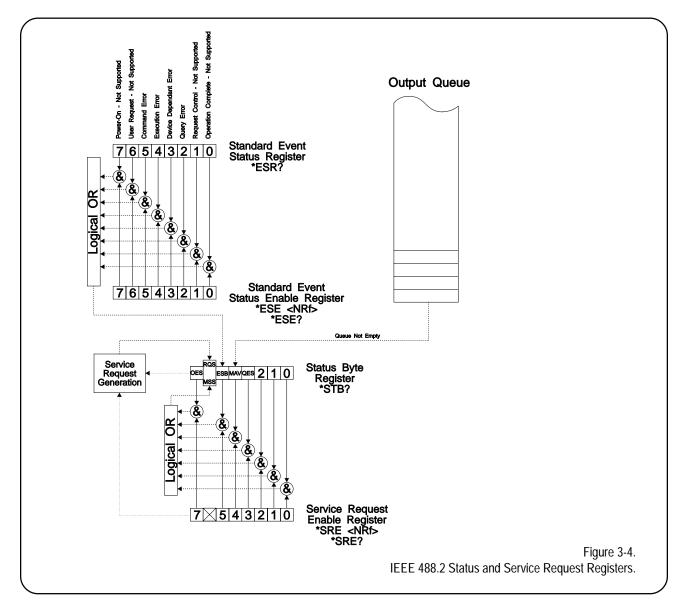

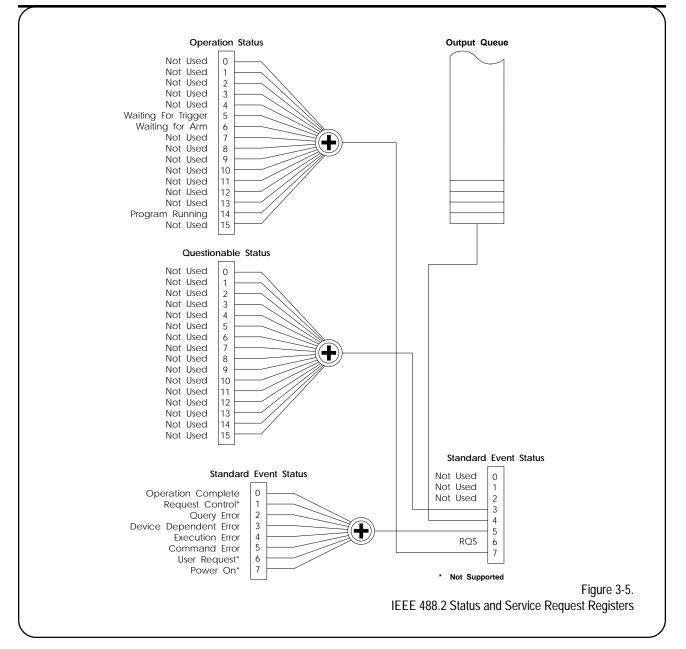

| Status Queries, Status Interrupts and System Queries                                                                                                                                                                                                                                                                  | 3-214                                                                                                                         |

| Status Queries, Status Interrupts and System Queries                                                                                                                                                                                                                                                                  | 3-214                                                                                                                         |

| Status Queries, Status Interrupts and System Queries<br>Operation Interrupt Definition                                                                                                                                                                                                                                |                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                       | 3-216                                                                                                                         |

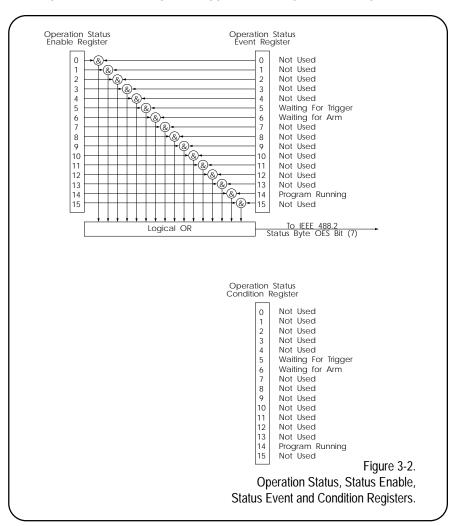

| Operation Interrupt Definition                                                                                                                                                                                                                                                                                        | 3-216<br>3-218                                                                                                                |

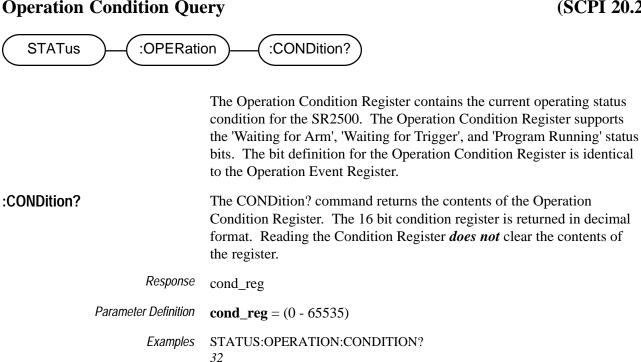

| Operation Interrupt Definition<br>Operation Condition Query                                                                                                                                                                                                                                                           | 3-216<br>3-218<br>3-219                                                                                                       |

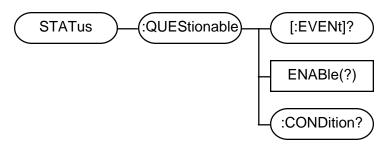

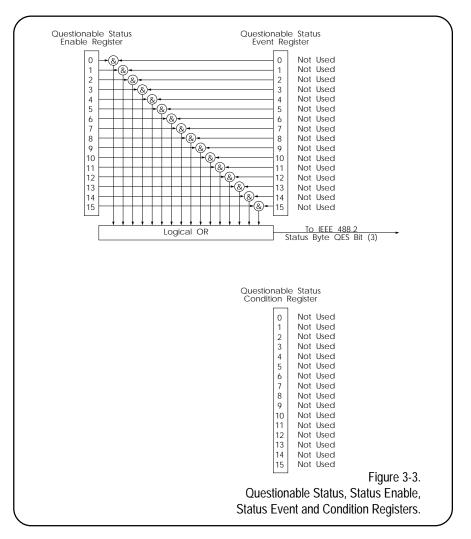

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers                                                                                                                                                                                                                          | 3-216<br>3-218<br>3-219<br>3-222                                                                                              |

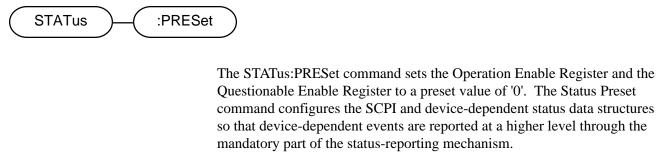

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset                                                                                                                                                                                                         | 3-216<br>3-218<br>3-219<br>3-222<br>3-223                                                                                     |

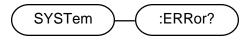

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset<br>System Error Query                                                                                                                                                                                   | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224                                                                            |

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset<br>System Error Query<br>SCPI Version Query<br>System IDN Query                                                                                                                                         | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225                                                                   |

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset<br>System Error Query<br>SCPI Version Query                                                                                                                                                             | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225                                                                   |

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset<br>System Error Query<br>SCPI Version Query<br>System IDN Query<br>Bus Master Time-Out                                                                                                                  | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225<br><b>3-227</b>                                                   |

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset<br>System Error Query<br>SCPI Version Query<br>System IDN Query                                                                                                                                         | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225<br><b>3-227</b>                                                   |

| Operation Interrupt Definition<br>Operation Condition Query<br>Questionable Status Registers<br>Status Preset<br>System Error Query<br>SCPI Version Query<br>System IDN Query<br>Bus Master Time-Out                                                                                                                  | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225<br><b>3-227</b><br>3-228                                          |

| Operation Interrupt Definition         Operation Condition Query         Questionable Status Registers         Status Preset         System Error Query         SCPI Version Query         System IDN Query         Bus Master Time-Out         Bus Master Time-Out         Variable Voltage I/O on the SR2500        | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225<br><b>3-227</b><br>3-228<br><b>3-228</b><br><b>3-229</b>          |

| Operation Interrupt Definition         Operation Condition Query         Questionable Status Registers         Status Preset         System Error Query         SCPI Version Query         System IDN Query         Bus Master Time-Out         Bus Master Time-Out         Selecting Response Threshold voltage Sets | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225<br><b>3-227</b><br>3-228<br><b>3-228</b><br><b>3-229</b><br>3-231 |

| Operation Interrupt Definition         Operation Condition Query         Questionable Status Registers         Status Preset         System Error Query         SCPI Version Query         System IDN Query         Bus Master Time-Out         Bus Master Time-Out         Variable Voltage I/O on the SR2500        | 3-216<br>3-218<br>3-219<br>3-222<br>3-223<br>3-224<br>3-225<br><b>3-227</b><br>3-228<br><b>3-228</b><br><b>3-229</b><br>3-231 |

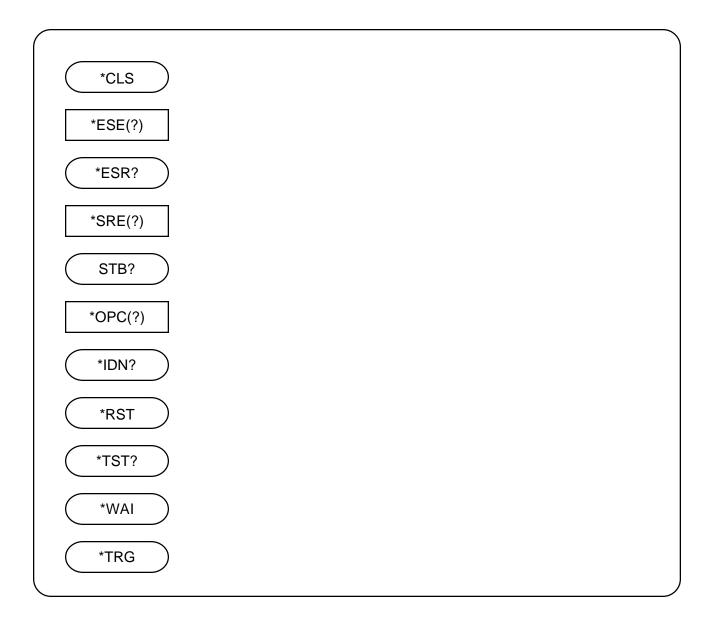

|                      | IEEE 488.2 Mandatory Commands                             | 3-236 |

|----------------------|-----------------------------------------------------------|-------|

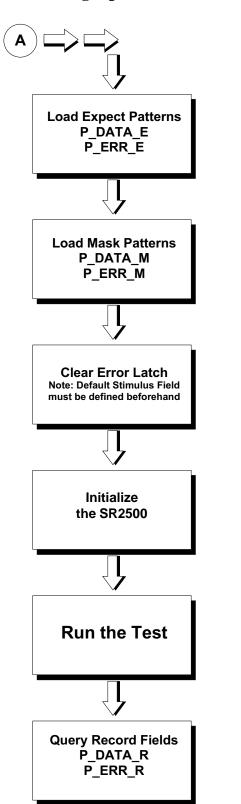

|                      | Programming Examples                                      | 4-1   |

| Chapter 4            | Program Steps                                             | 4-1   |

| Programming Examples | RAM-Backed Pattern Generation                             | 4-7   |

|                      | Using CMACROS and Data Formatting                         | 4-10  |

|                      | Generating Algorithmic Stimulus Patterns                  | 4-13  |

|                      | Using Real-Time Compare and Algorithmic Expcted Responses | 4-19  |

|                      | Recording UUT Responses                                   | 4-26  |

(THIS PAGE INTENTIONALLY LEFT BLANK)

#### CHAPTER 1

## **General Information**

**About This Manual**

This manual provides installation and operation information for the Interface Technology SR2500 VXI Digital Test Subsystem Information contained herein is intended for use by technical personnel involved in the actual installation and operation of the subject equipment.

#### Arrangement of Manual

This document is comprised of five separate manuals as follows:

- o SR2500 User's Manual (overall system manual)

- o SR2510 User's Manual

- o SR2520 User's Manual

- o SR2520 Guided Probe Option User's Manual (option)

- o RG2500 Rail Generator User's Manual (option)

#### Arrangement of Contents, This Manual

Information contained in this manual is arranged in four chapters, as follows:

- o Chapter 1 General Information

- o Chapter 2 Test Programming Parameters

- o Chapter 3 Programming

- o Chapter 4 Programming Examples

#### Applicability

The information contained in this manual covers a single equipment configuration designated *SR2500 VXI Digital Test Subsystem*. Differences, if any, between this equipment and the actual equipment supplied are covered by Difference Data included at the front of this manual.

#### Supersedure Notice

This manual supersedes SR2500 User's Manual, Rev.04 and all previous issues of this publication.

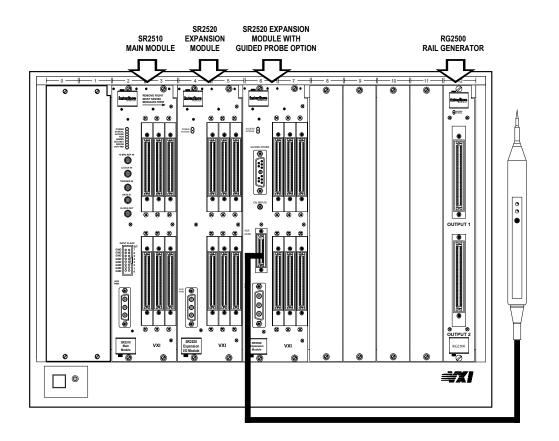

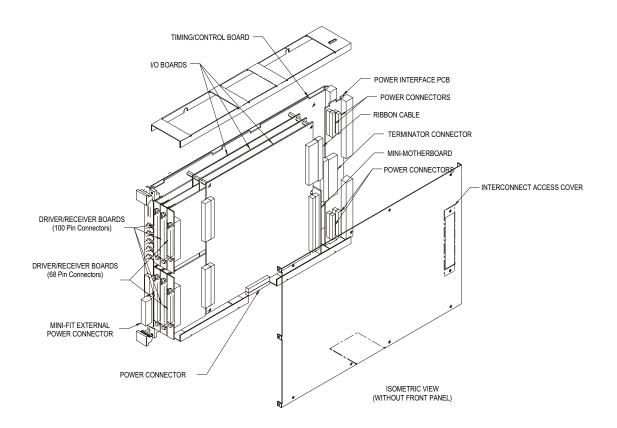

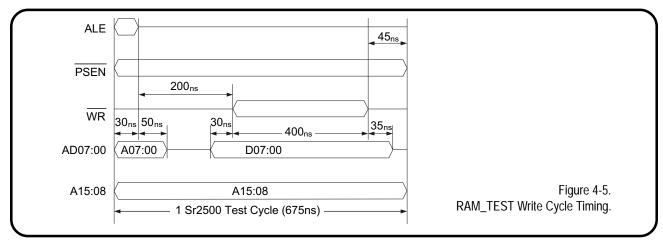

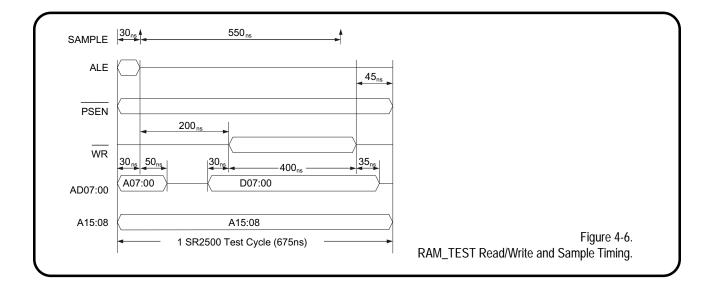

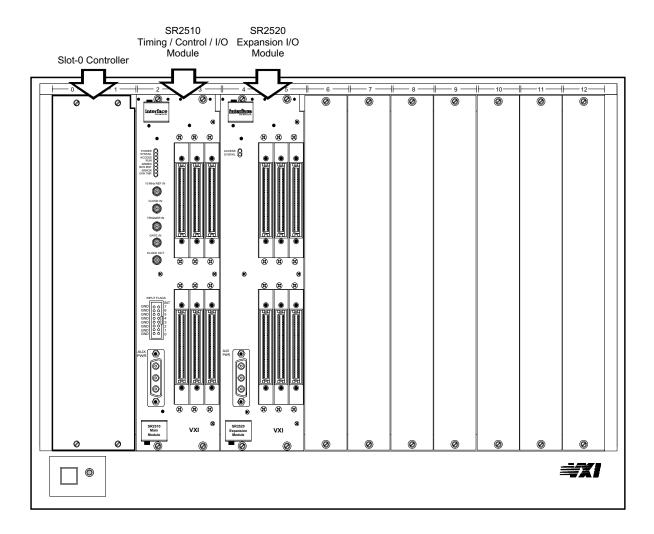

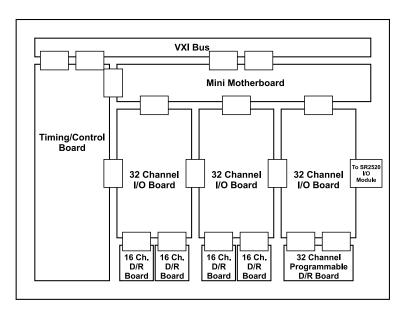

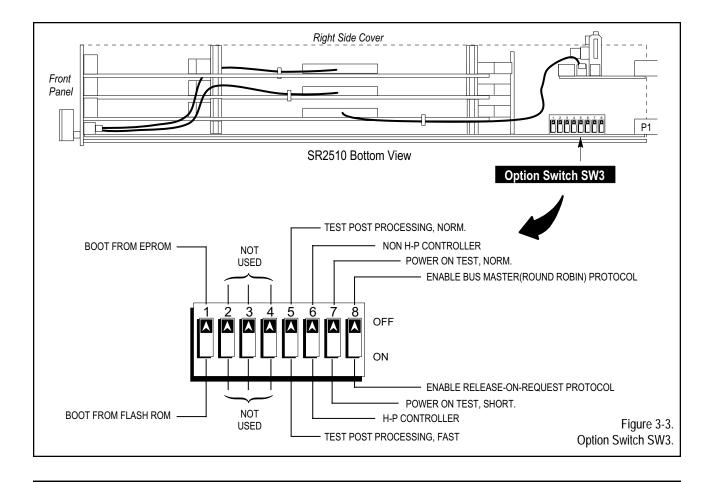

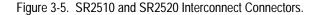

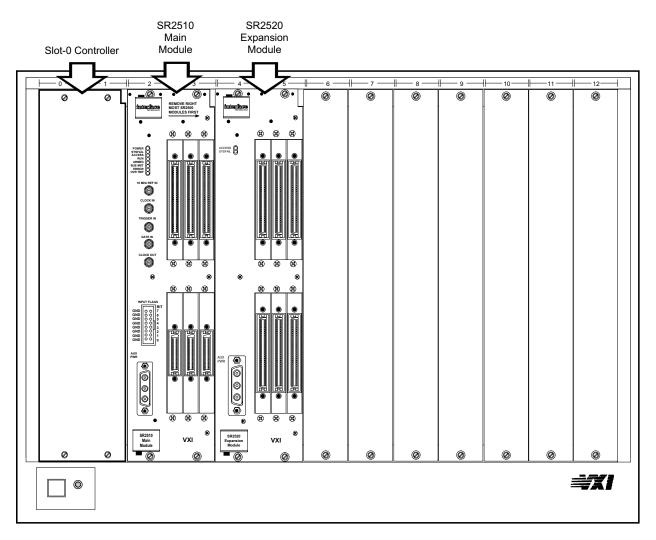

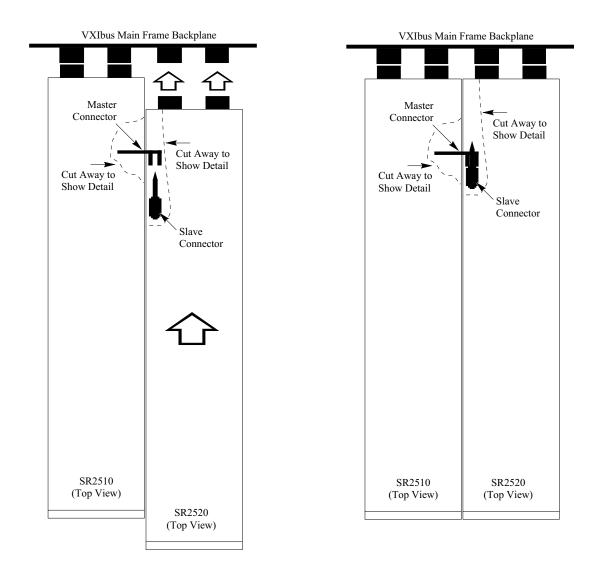

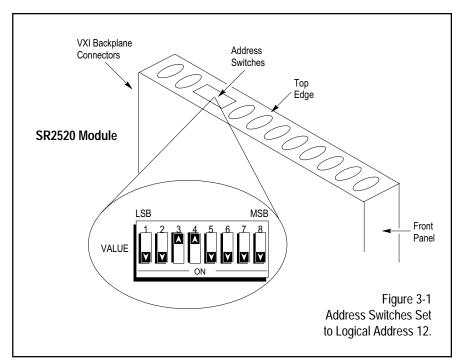

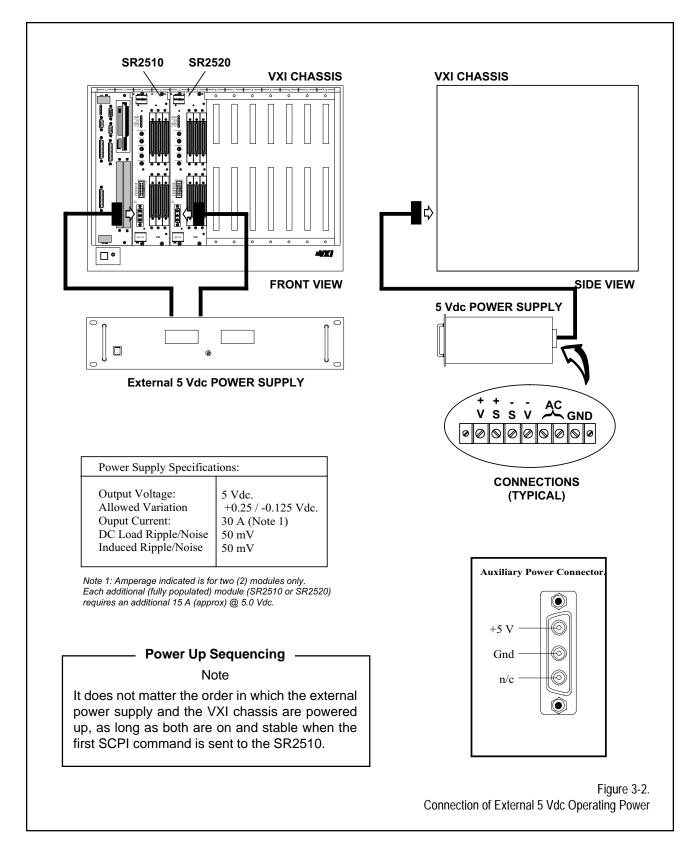

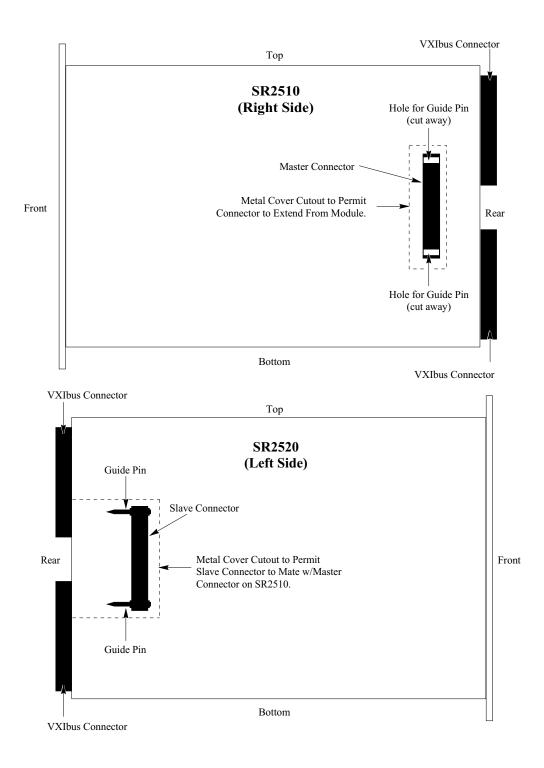

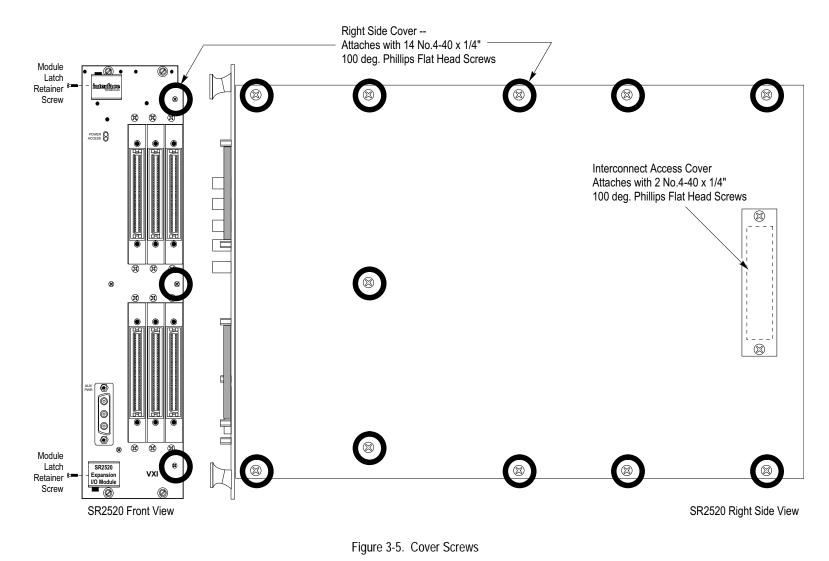

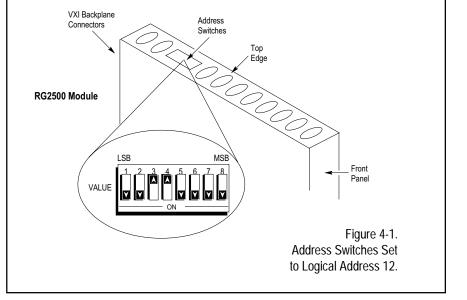

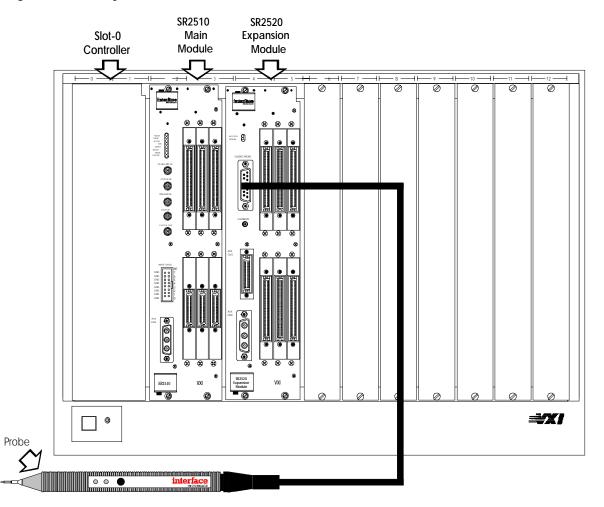

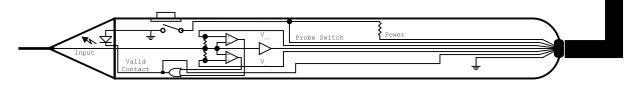

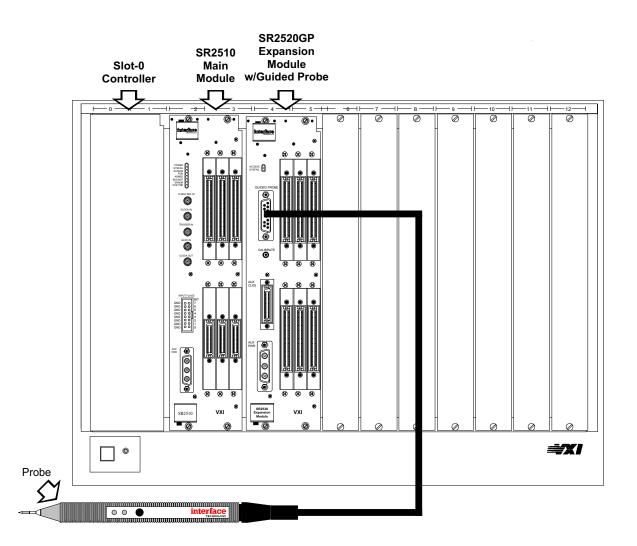

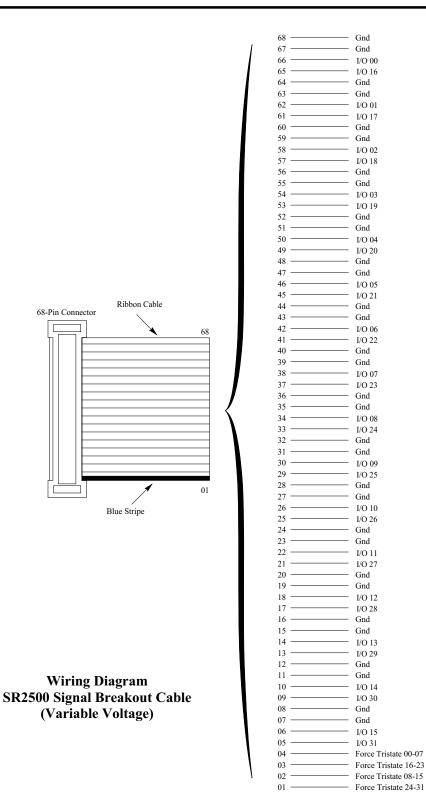

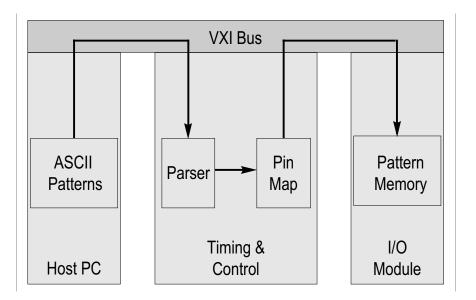

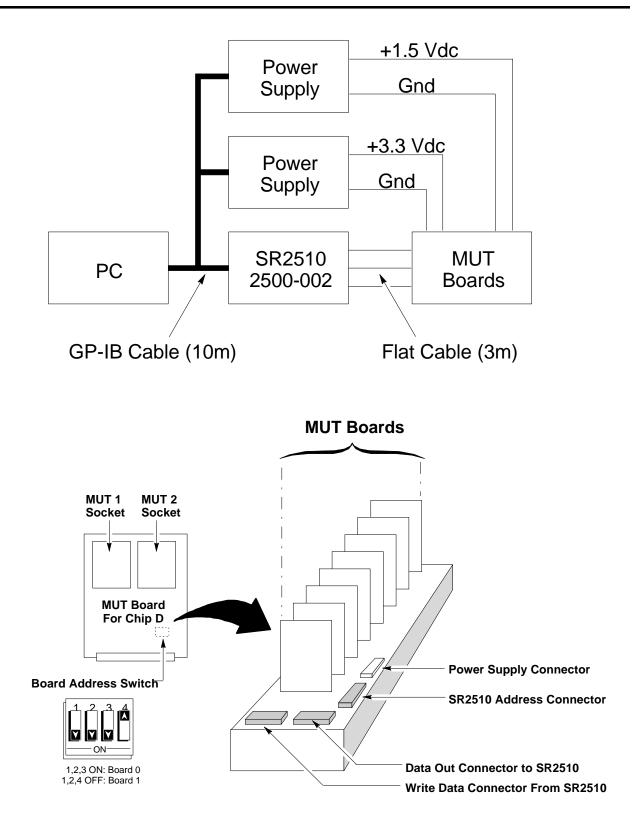

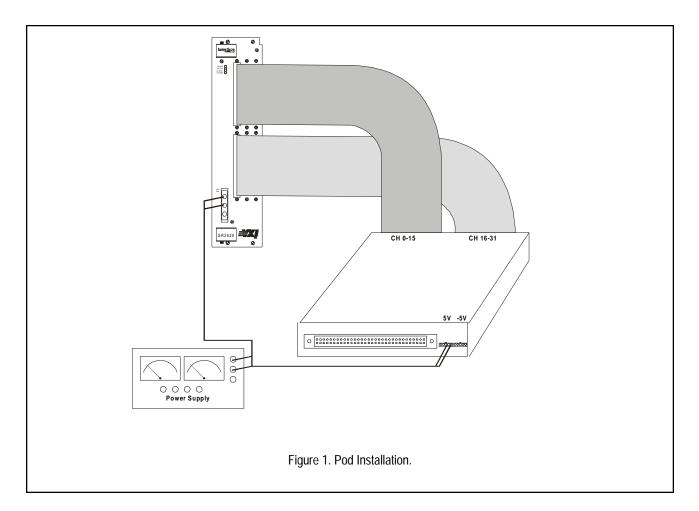

Equipment DescriptionThe SR2500 Digital stimulus/response Subsystem provides DC to 25 MHz<br/>digital logic patterns for serial and parallel testing of digital semiconduc-<br/>tor devices, ASICs, components, circuit boards, assemblies, and other<br/>digital devices including complete digital systems. Based on the industry<br/>standard VXI architecture, the SR2500 digital subsystem is comprised of<br/>one or more dual-slot C-size modules as shown in Figure 1-1.

Figure 1-1. SR2500 VXI Digital Test Subsystem.

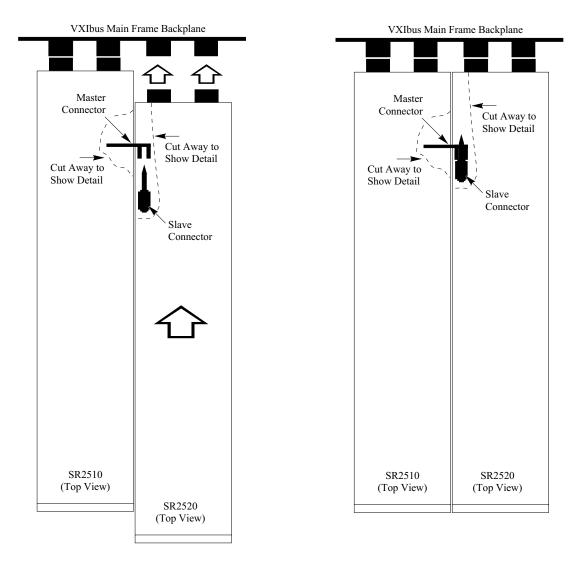

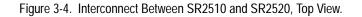

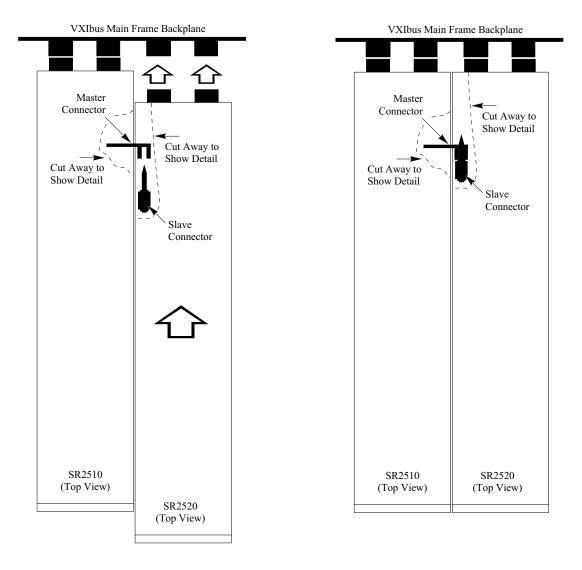

The major components of the SR2500 VXI Digital Test Subsystem are the SR2510 Main Module and one or more optional modules used to enhance or expand the subsystem. The optional modules include the SR2520 Expansion Module, the RG2500 Rail Generator, and a Guided Probe option for the SR2520 Expansion Module.

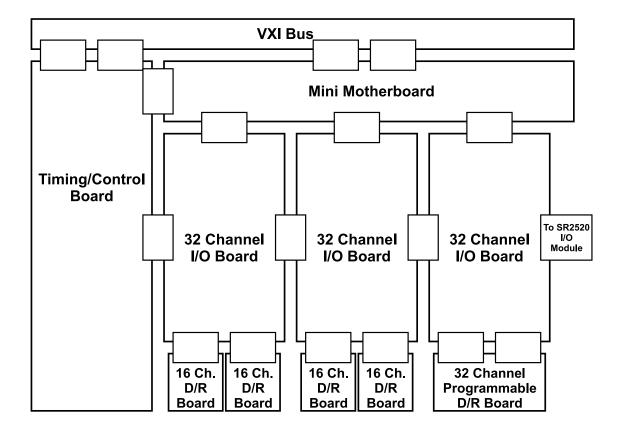

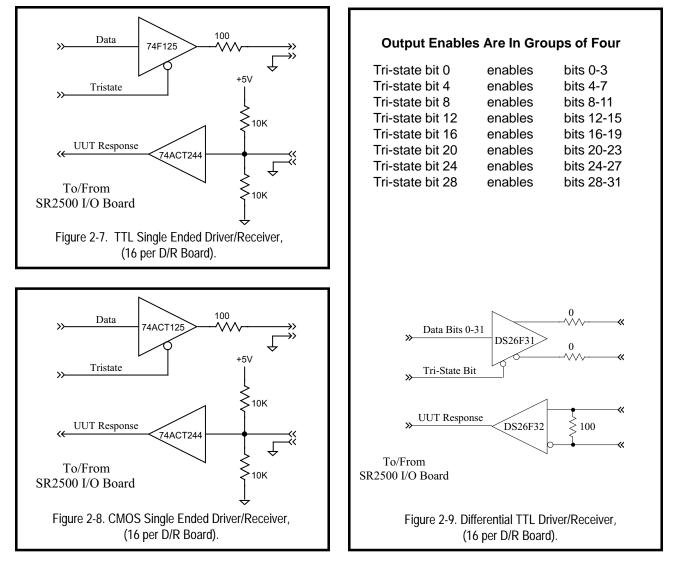

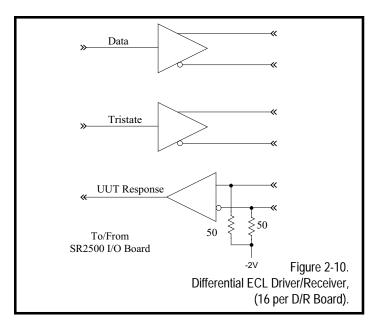

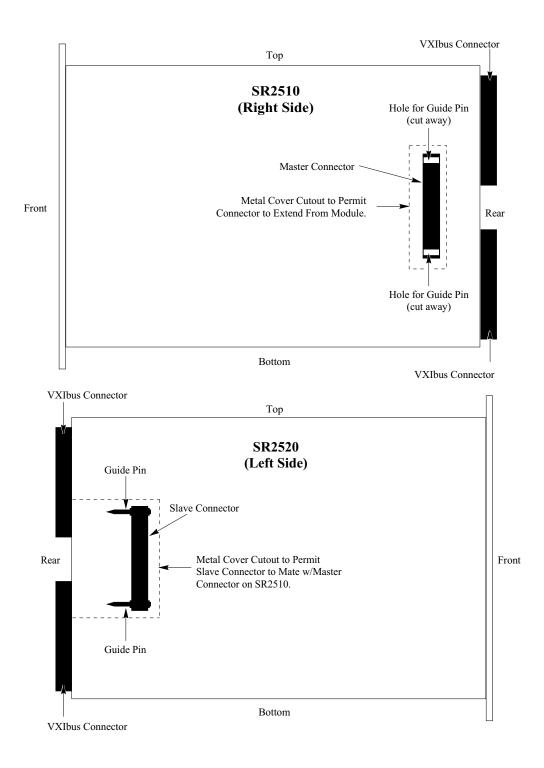

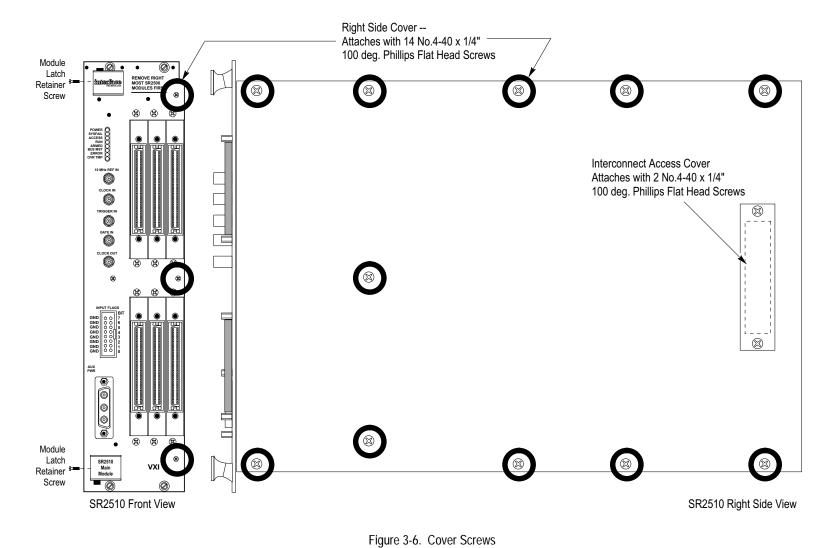

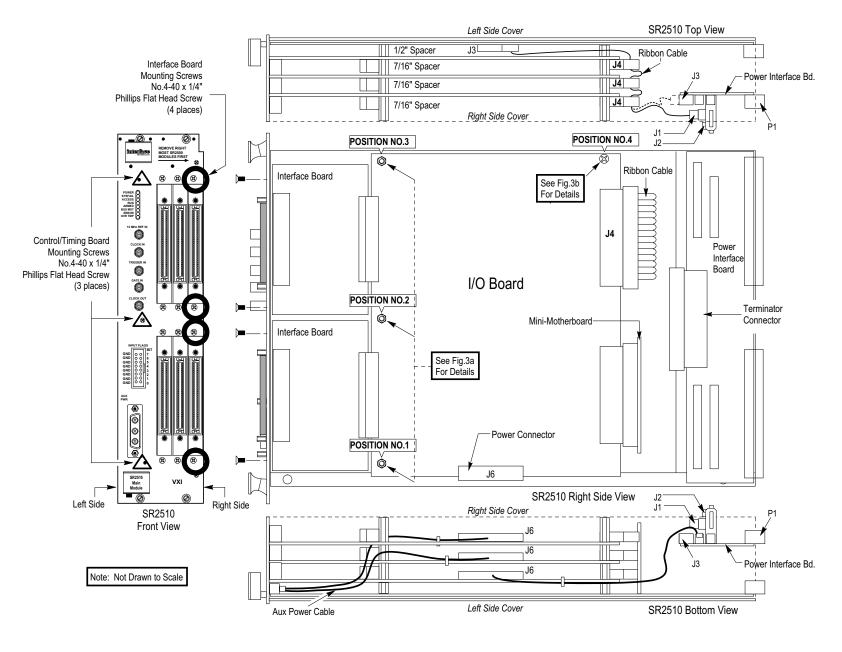

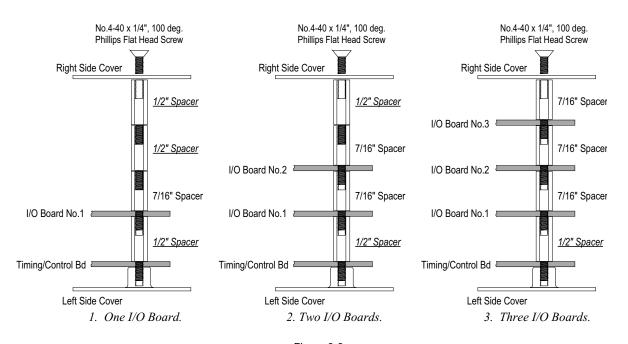

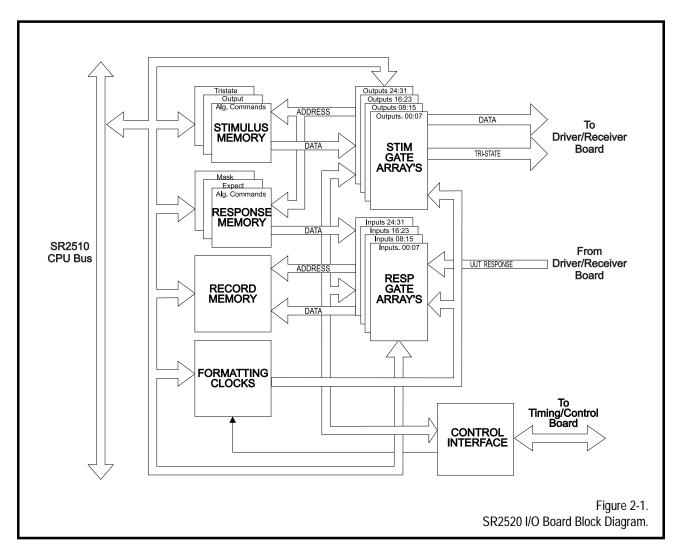

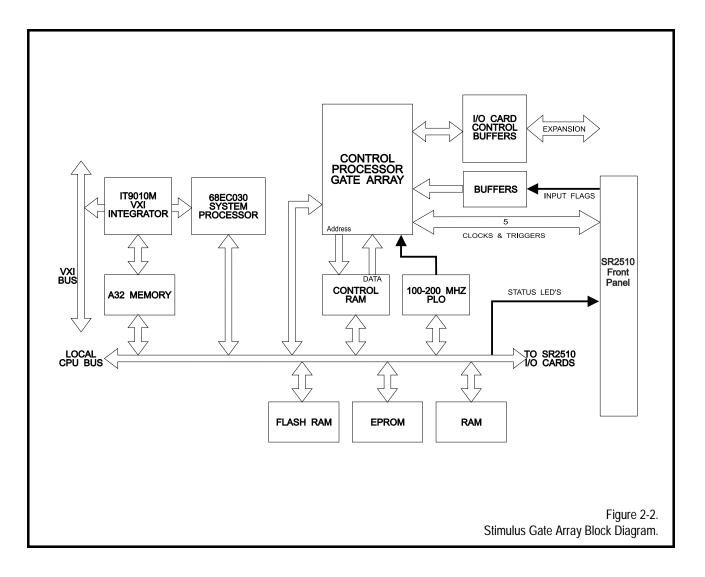

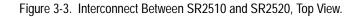

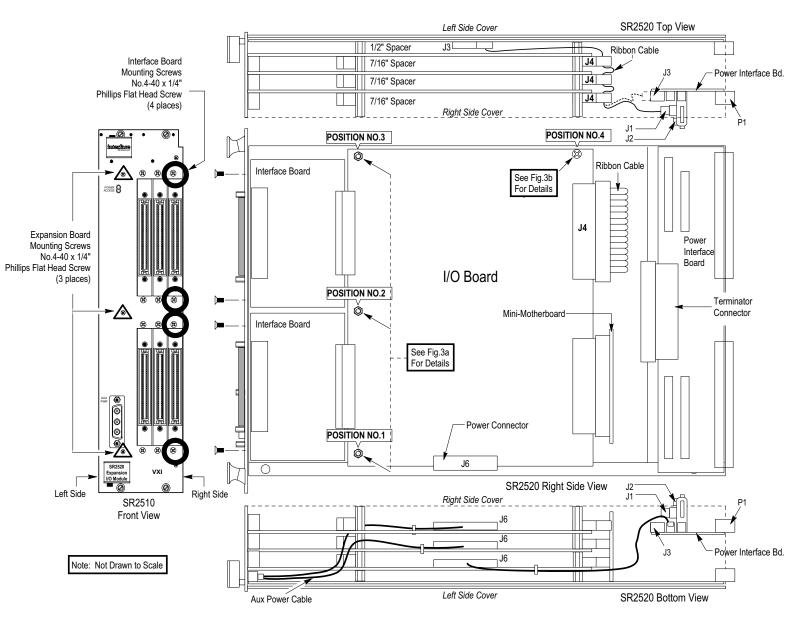

#### SR2510 Main Module

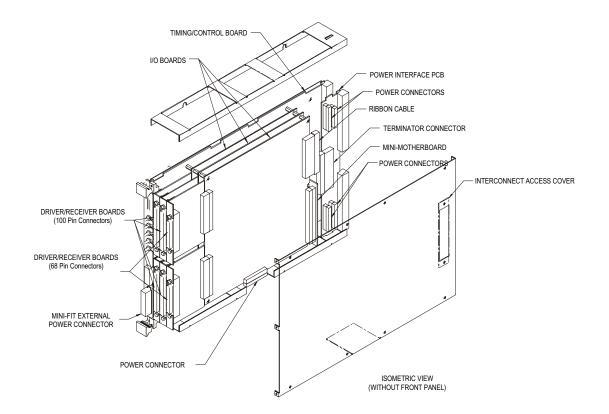

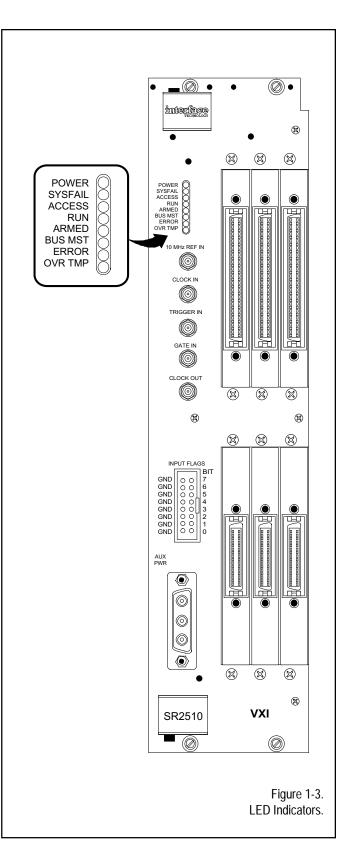

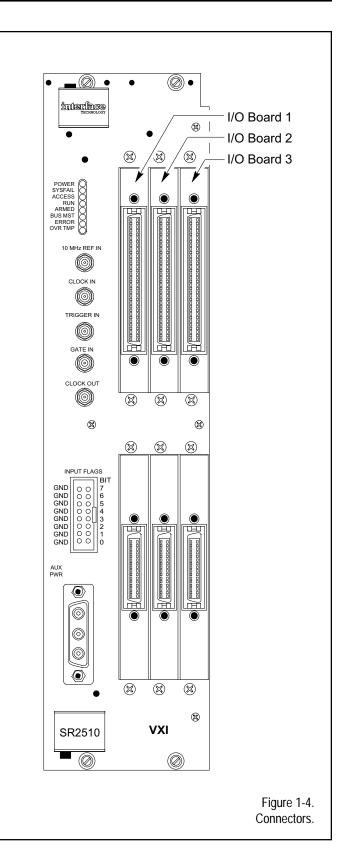

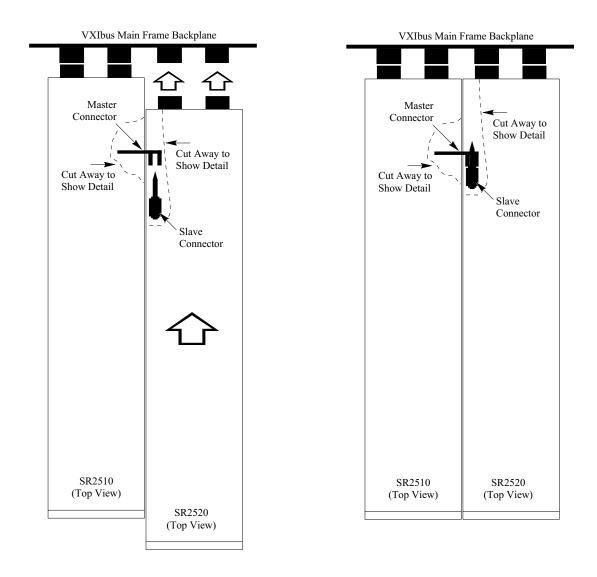

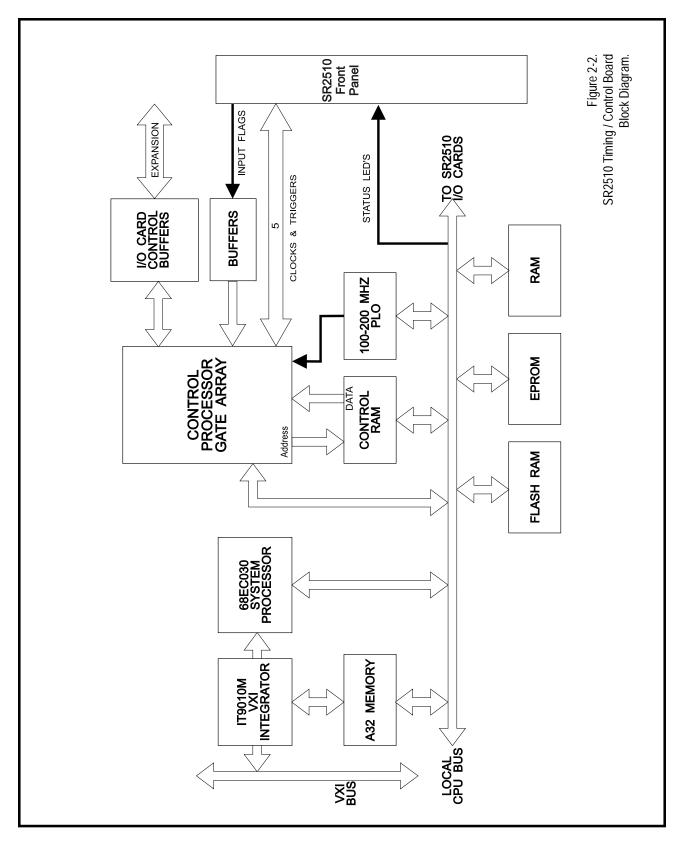

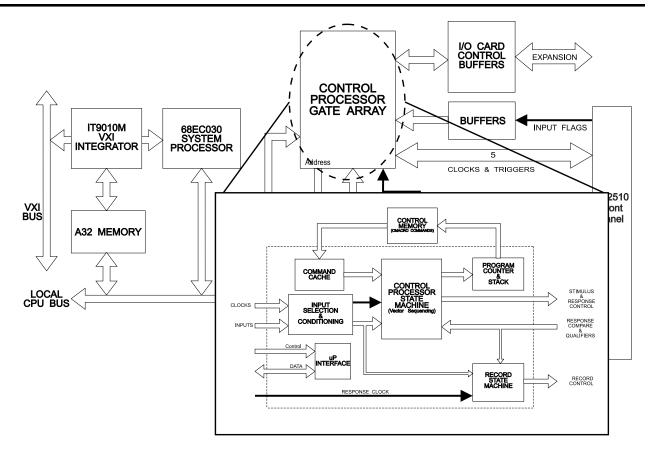

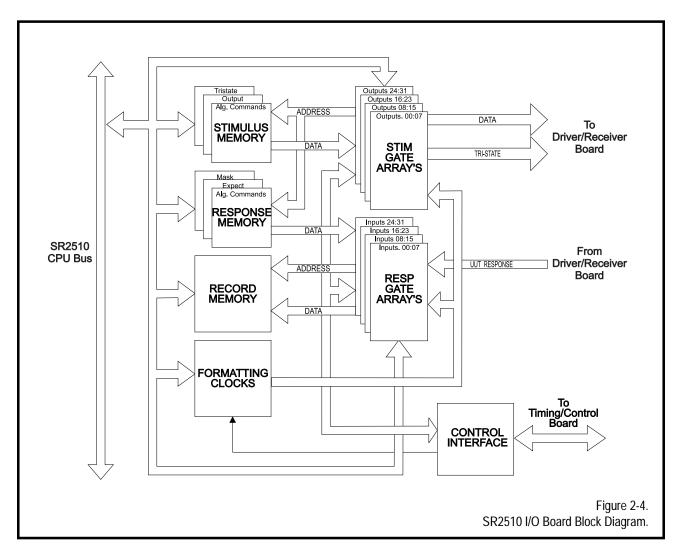

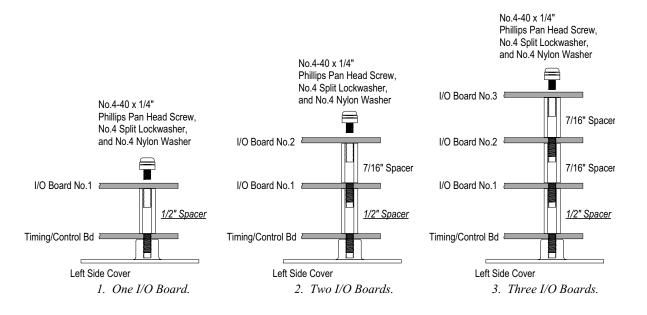

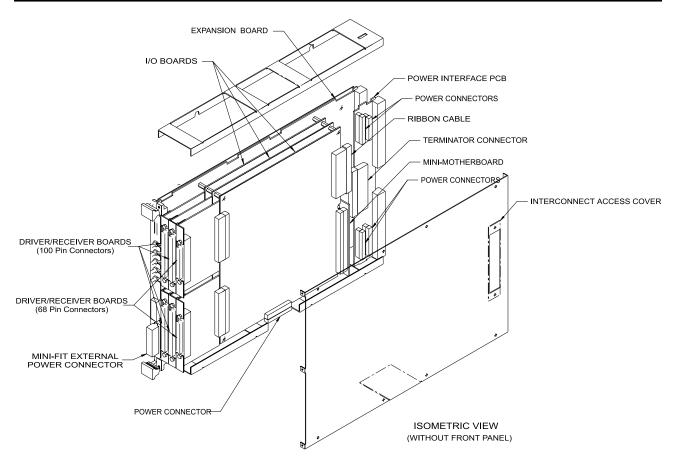

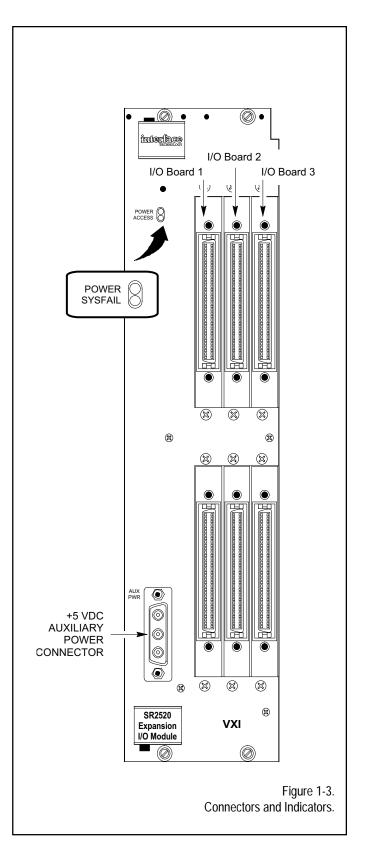

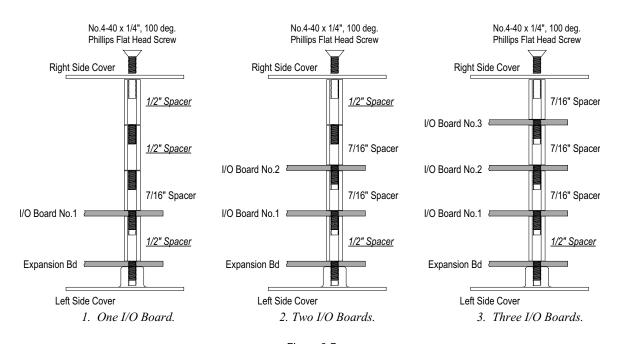

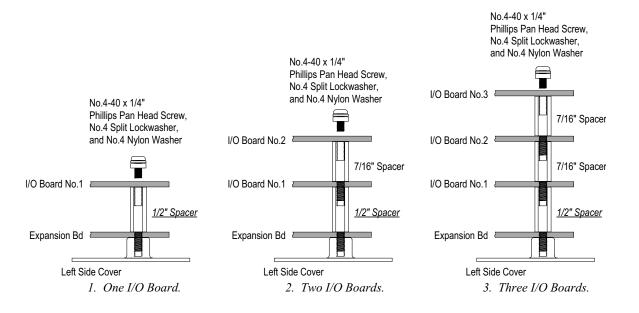

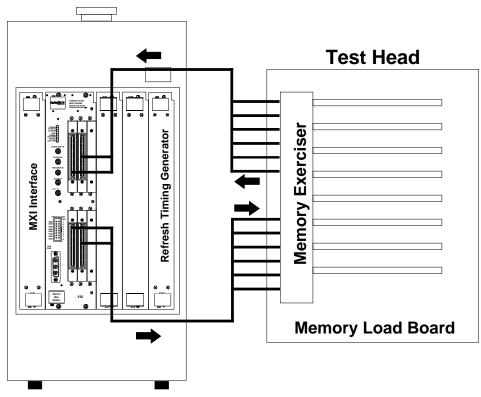

The message-based SR2510 provides clocking and test sequence control functions for all I/O channels within the SR2510 module, and for all SR2520 Expansion Modules as well. The SR2510 consists of a Timing/ Control board, up to three (3) I/O boards, up to six (6) Driver/Receiver boards (two per I/O board) and boards for timing distribution, power distribution and interface logic for any SR2520 expansion modules, see Figures 1-2 and 1-3. The Timing/Control board contains a 25 MHz 68EC030 microprocessor (system processor) that provides the basic user interface to the SR2500 system. The 68EC030 parses and interprets the VXI word-serial commands and provides overall system setup and test monitoring. The SR2510 also contains a custom control processor ASIC that provides real-time control over the test pattern sequencing. The control processor is capable of providing sequential or nested program looping and conditional or unconditional jumps and subroutines. Overall test timing is provided by a programmable 200 Hz to 25 MHz frequency synthesized clock source as well as external inputs for clocks, gates, test inputs and triggers. For additional details, refer to the *SR2510 User's manual*.

Figure 1-2. SR2510 Main Module, Exploded View Showing Major Components.

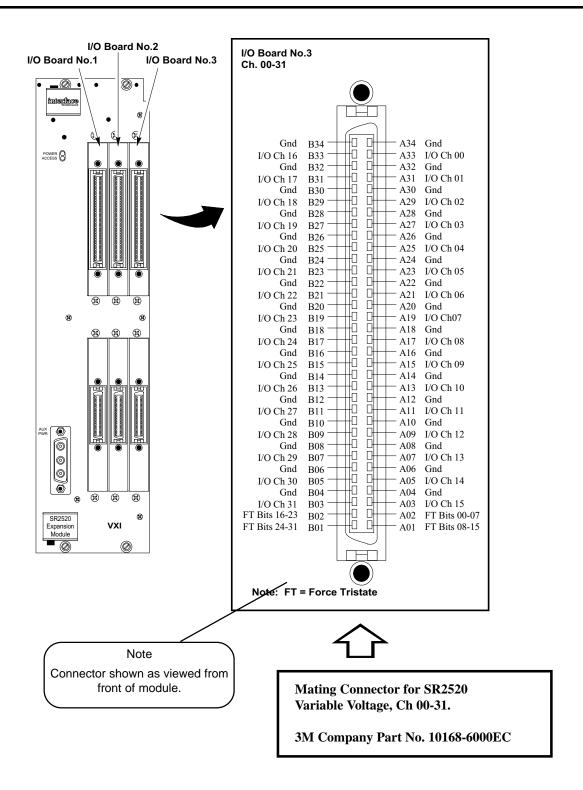

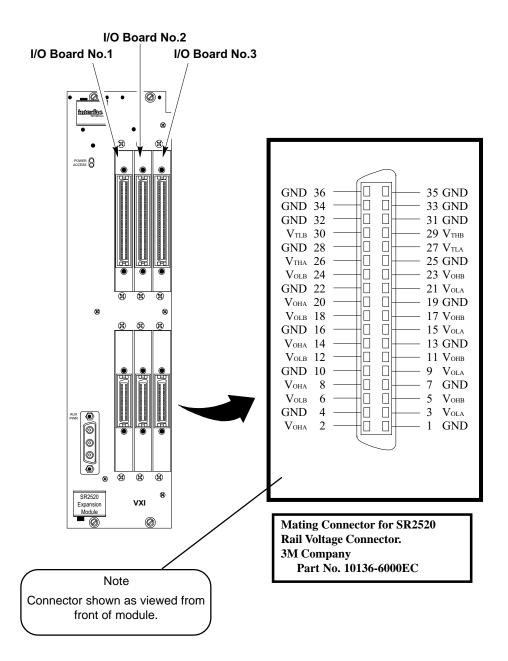

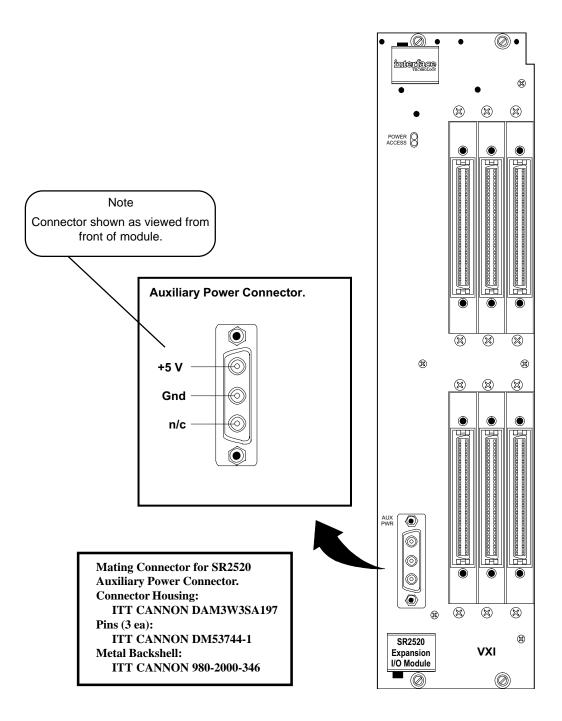

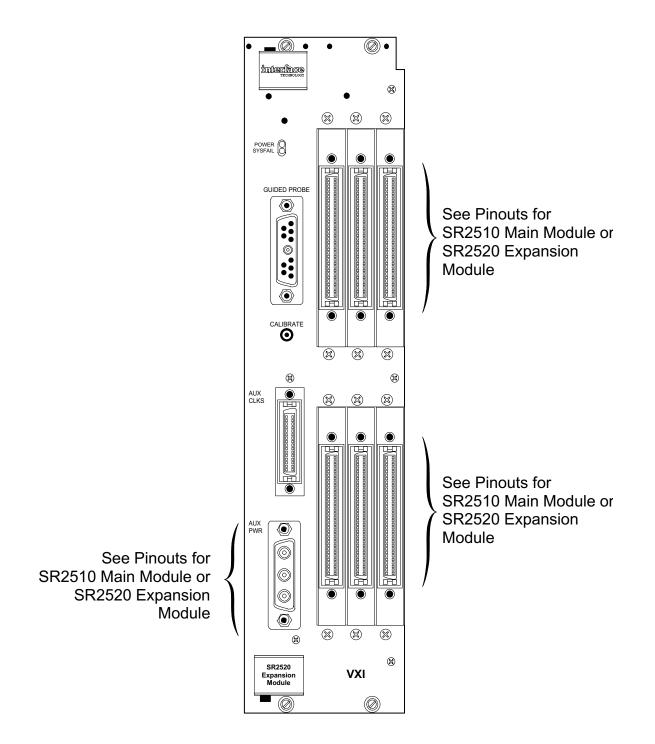

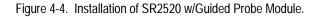

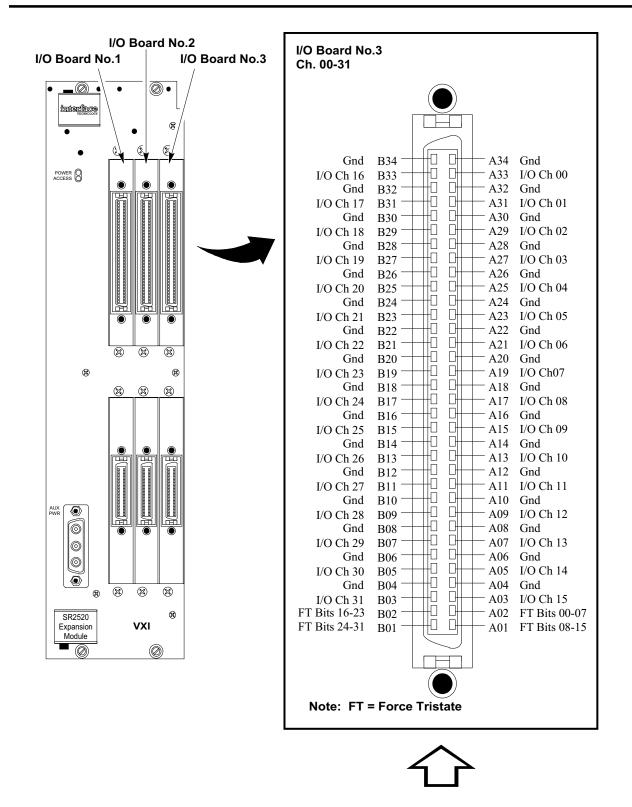

#### SR2520 Expansion Module

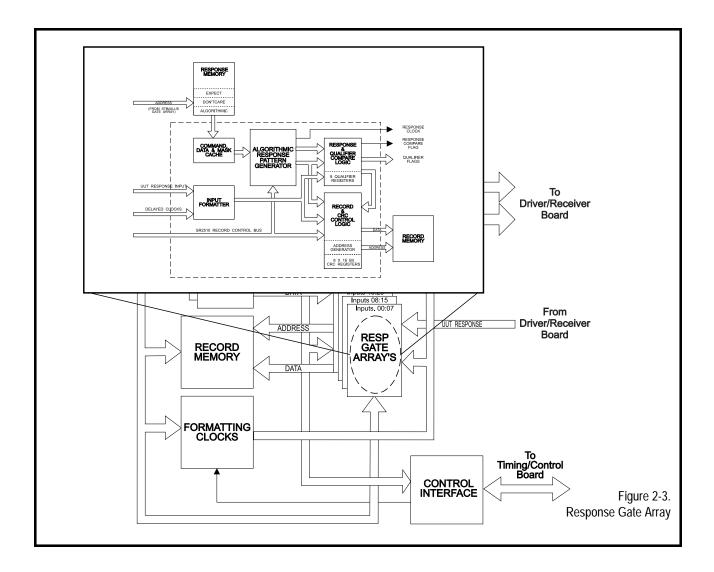

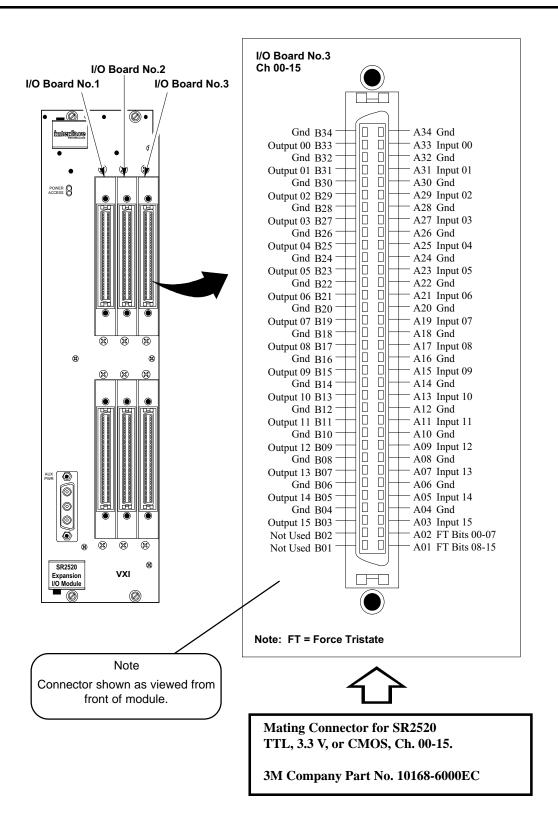

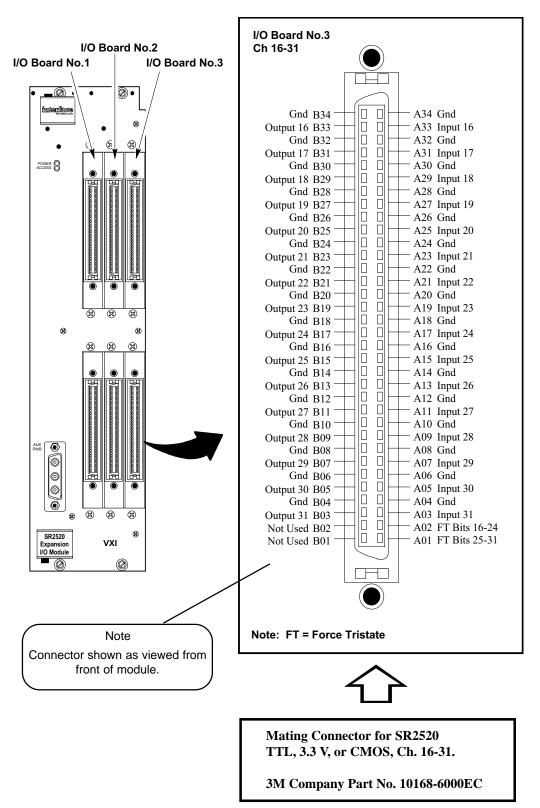

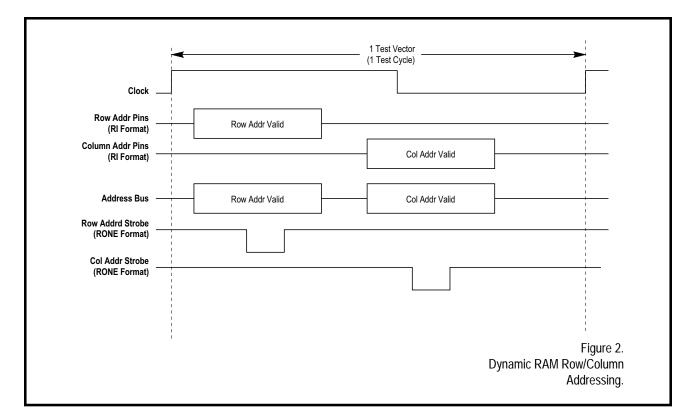

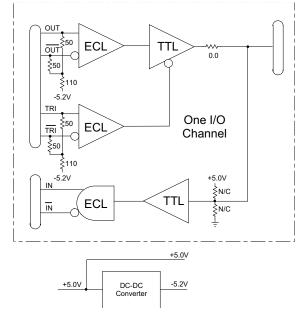

(See Fig 1-1) The SR2520 expansion module is a register-based companion to the SR2510 module. Each SR2520 provides an additional 96 I/O channels, and up to five SR2520s (up to 576 channels) may be included in a single SR2500 subsystem. Each SR2520 module has 96 output pins and 96 input pins, except in the case of the Variable Voltage configuration, which has 96 bi-directional I/O pins. By connecting the output and input pins together, 96 I/O channels can be realized. Each I/O channel generates digital stimulus patterns, provides real-time comparison capabilities on the response inputs, and contains logic analyzer type triggering and data recording functions, all at speeds up to 25 MHz.

Except in the case of the Differential ECL configuration, which has no tristate memories, each stimulus pin contains output and tristate memories, allowing bi-directional signal paths. The response pin provides *expected response* and *mask* ("don't care") memories, which generate the expected input pattern used for the real-time comparison. The logic analyzer triggering and recording subsystem allows the recording of either the actual input pattern or the results of the real-time comparison of the expected response pattern and the input pattern (error data). Either may be saved and then later retrieved from the record memory, in much the same way you would use a logic analyzer.

The SR2500 subsystem is designed to operate with any VXI compatible slot-0 controller that supports the word serial protocol. The command set that controls test setup and execution is based on the SCPI-syntax command set.

#### Interface Technology

Figure 1-3. Block Diagram, SR2510 Major Components.

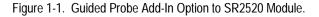

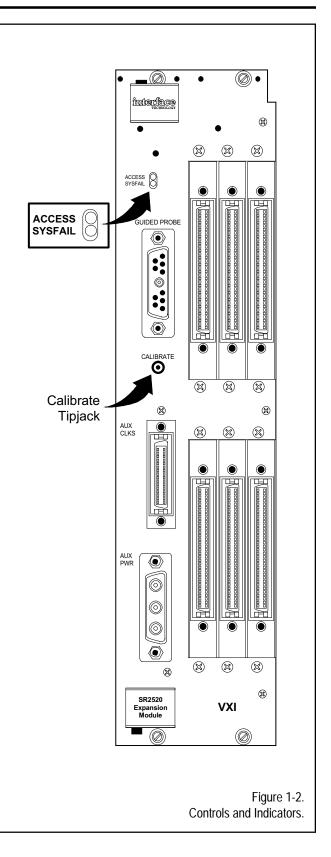

#### SR2520 w/Guided Probe (option)

(see Fig 1-1) Guided Probe is supplied as a factory installed, add-in option to the SR2520 Expansion Module. This option provides the user with the capaiblity to read test points (nodes) on the UUT to determine pass/fail conditions. The guided probe is capable of testing and detecting high, low, and indeterminate states and can also measure analog voltages. Upon determination of the pass/fail state, the guided probe stores the UUT response along with the compare results for later readout. The probe has an active input, which minimizes circuit loading and serves to "condition" the UUT signal before routing it to the guided probe logic. Located on the probe body is an ENTER button used to trigger or continue test execution. For additional details, refer to the *SR2520 Guided Probe Option User's Manual*.

#### **RG2500 Rail Generator (option)**

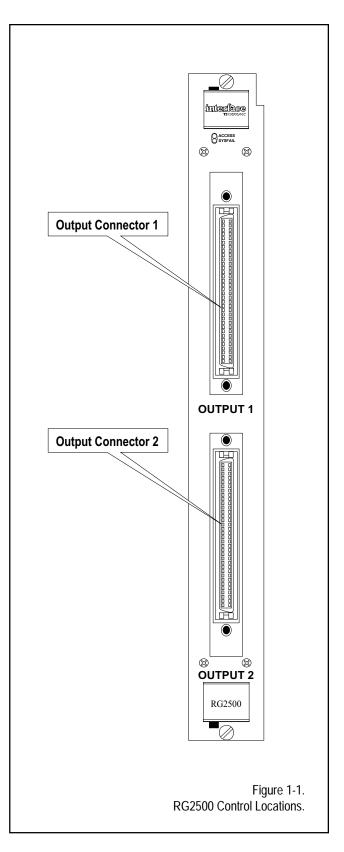

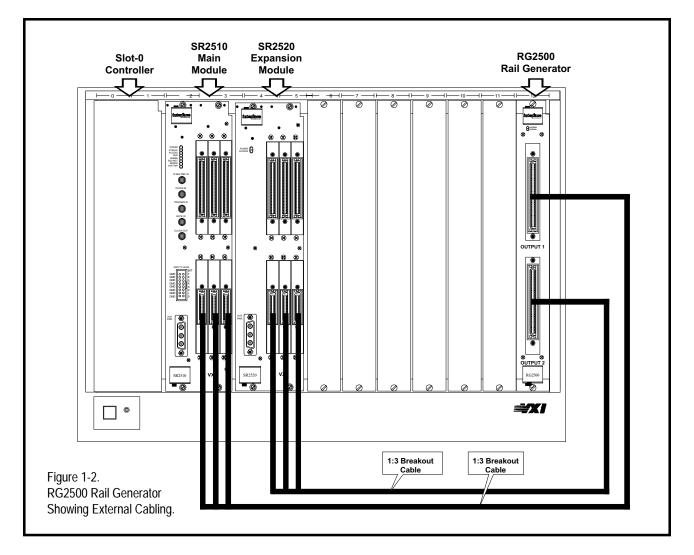

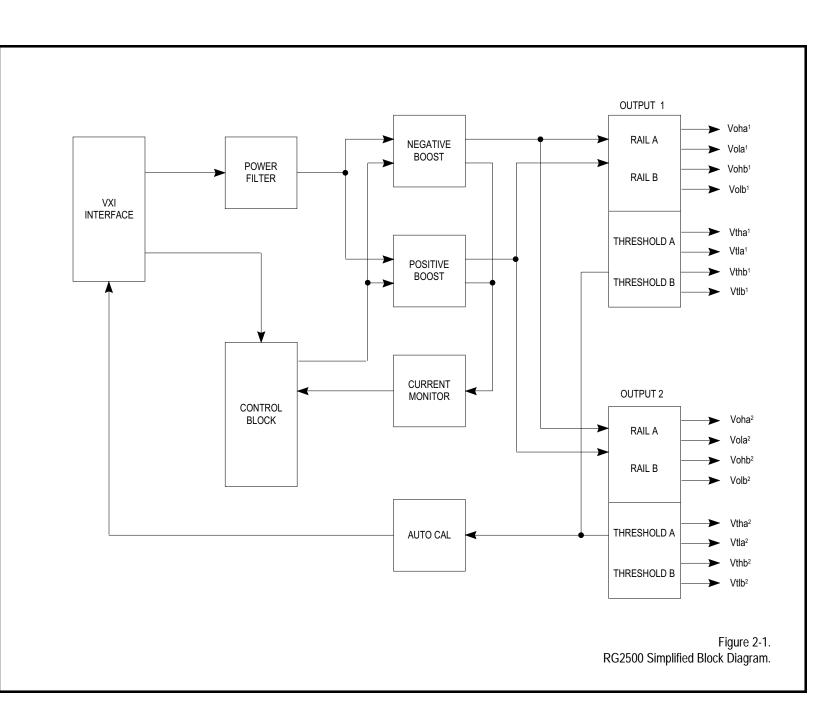

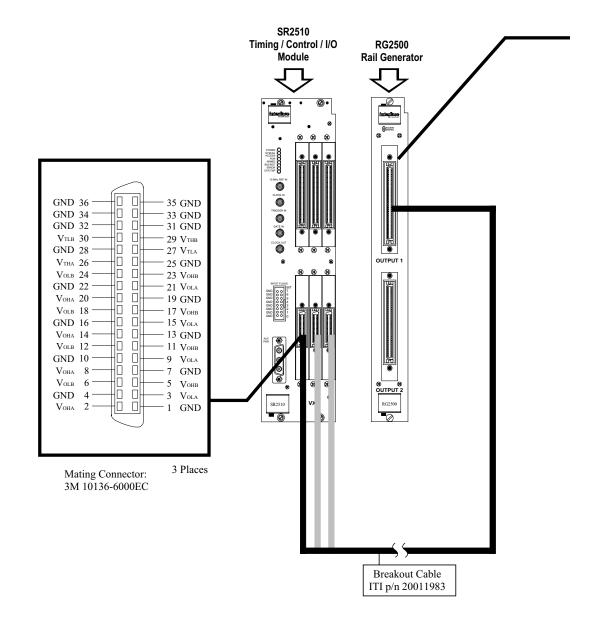

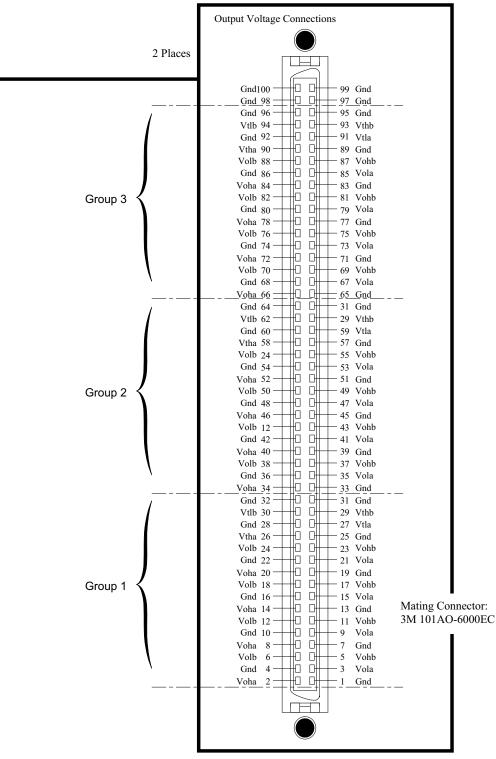

(See Fig 1-1) The RG2500 Rail Generator is a programmable power supply used to provide operating voltages to the SR2510 and SR2520 modules whenever these modules are configured for programmable (variable voltage) operation.

The RG2500 receives operating voltages and control commands from the host computer and supplies either one or two SR2510 or SR2520 modules with eight individual output voltages, each of which is separately programmable over a range of -3.0 to +7.0 Vdc. For additional details, refer to the *RG2500 User's Manual*.

#### CHAPTER 2

## **Test Programming Parameters**

**Test Programs**

Fields

The SR2500 subsystem is capable of storing multiple user-defined, userselectable tests in memory. Each test contains complete setup information for test size, field definitions, system timing, input and output formats, record control and stimulus and response data. The maximum tests that may be stored in memory is 128, or until all I/O memory is used up, whichever occurs first. Each time a test is defined, a size (in vectors) must be specified, which causes I/O resources to be allocated for that test. The test size must be an even number of vectors and the actual resources allocated is the size defined plus some internal overhead (up to 32 vectors). Each test retains pointers to its own stimulus/response memory segment, as well as its own unique settings for fields, output format, signal conditioners, etc.

For example, if a test is defined with a size of 100, then 100 I/O vectors are allocated to that test. The available free I/O memory is reduced by 100. This process may be repeated until either 128 tests have been defined, or all of the available I/O memory has been used. If a test is later deleted, then software housekeeping automatically reallocates all of the remaining test resources to keep the unused resources in a sequential address space. The user may select a previously defined test, for execution or modification, via a simple command. Once the user selects a test, system access is directed to the currently active test. The user may also query the system to determine the loaded tests and the status of all defined tests.

Access to the test's stimulus/response memory is based on "fields." By definition, a field is a logical group of stimulus, response or record pins. Before data can be loaded to or queried from an SR2500 module, the user must create a field. Fields are created by defining:

- o a unique field name

- o a field type

- o the I/O pins associated with that field.

Field width is limited to a maximum of 32 pins. Once a field is defined, the pins associated with that field are not dedicated to only that field. It is possible to define many fields, each containing a pin that was previously defined in another field, or fields. This is very useful for setting up fields and sub-fields. For example, you may define a 4 bit "control" field and a 16 bit data field, and a third field that is 20 bits wide consisting of both control and data. This can be very useful for display purposes, since both control and data may be read with a single command, while retaining the flexibility of manipulating each field independently of the other.

There are three basic field types:

- o stimulus

- o expected response (response)

- o record

There are also sub-types for *stimulus* and *response* fields. Three of the sub-types for *stimulus* and *response* fields are

- o non-algorithmic

- o algorithmic

- o hardware

#### **Non-Algorithmic Fields**

Non-algorithmic fields generate their patterns from data stored in RAM. For this reason they are often called RAM-backed patterns. Non-algorithmic fields are very flexible, since pins in a non-algorithmic field can be assigned in any order and any MSB/LSB designation.

#### **Algorithmic Fields**

Algorithmic fields generate their patterns algorithmically from a simple set of commands. Test sequences that ordinarily consume excessive amounts of stimulus/response memory can be reduced to just a few algorithmic commands. For example, the "walking bit" data pattern and "incrementing address" patterns often used to functionally test RAM would use proportionately large amounts of stimulus/response memory. The larger the RAM being tested, the more RAM-backed test vectors that would be required. Using algorithmic fields, a single vector of stimulus/ response memory can generate up to 65,536 unique address/data vectors. By placing the algorithmic command within nested loops, literally billions of unique address and data test vectors may be generated using only a few actual vectors.

Because algorithmic patterns are generated in hardware, several restrictions exist concerning how these fields can be assigned. An algorithmic field must consist of byte wide groups of 8, 16, 24 or 32 pins and the MSB/LSB ordering is fixed. None of these restrictions exist for nonalgorithmic fields.

One of the algorithmic commands supported allows data to be output from memory, exactly as a RAM-backed field works. This allows mixing of algorithmic and RAM-backed pattern generation on the same pins, but at different test vectors (cycles).

#### Hardware Fields

|                   | Hardware type fields allow loading of data directly to I/O RAM, bypass-<br>ing the field pin mapping algorithms and the associated processor over-<br>head. By eliminating this overhead, data can be loaded to hardware type<br>fields faster than loading data to other field types. As already discussed<br>above, a pin, or group of pins, may be mapped to multiple fields. So pins<br>may be associated with non-hardware type fields for convenience, and<br>simultaneously associated with hardware type fields for improved perfor-<br>mance in querying and loading data patterns.                                                                                                                                                                                                                                                                  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vector Looping    | A section of stimulus/response memory may be repeatedly looped many<br>times, as determined by a loop count value or by various test conditions.<br>The loops are described as "seamless" because no extra test cycles are<br>required when the program jumps from the bottom of the loop to the top.<br>There are two loop types, <i>word loops</i> , which loop on a single test vector,<br>and <i>start/end loops</i> , which loop through a range of vectors. Start/end<br>loops may be nested two levels deep, and the nesting must be in a linear<br>sequence of vectors. In other words, with nested start/end loops, it is not<br>allowed to have the first level of looping in the main program sequence,<br>and the second level of looping located within a subroutine. Any number<br>of word loops may be placed within the start/end loop range. |

|                   | <ul> <li>Two other loop structures are provided in the SR2500 subsystem. One is the <i>program loop</i>, the other is the <i>arm count</i>. With program loops, the entire test program may be repeated up to 65,536 times or continuously. The arm count defines the number of times the SR2500 will re-arm itself and wait for a system trigger. After the trigger, the SR2500 will run through it's entire test sequence as many times as defined with the program loop. Then, assuming the arm count has not been reached, the SR2500 will automatically re-arm itself. Another trigger will cause the test to run again. This process continues until the SR2500 test has run the number of times specified by the arm count value.</li> </ul>                                                                                                           |

| Program Branching | The SR2500 test program allows conditional and unconditional test<br>branching. During a <i>branch</i> , the data value on the output pins will remain<br>from the test vector immediately prior to the branch instruction. The user<br>has the option of keeping the stimulus data formatting active (useful for<br>keeping clocks active) or suppressing it during the branch, in which case<br>the output pins remain static during the branch. There are three branch<br>types, as follows:                                                                                                                                                                                                                                                                                                                                                               |

|                   | CJMP   JMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | <b>CJMP</b>   <b>JMP</b> allows the test to conditionally or unconditionally branch to any vector location within a test. Test sequencing and pattern generation will continue from the new vector. Jumps to an odd vector require (4) test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

cycles, while jumps to an even vector requires (5) cycles.

#### CJSRoutine | JSRoutine

| Rev. 05                    | Interface Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Using a <i>return-to</i> format, the user can control both the delay and the width of the output format. The delay represents the point at which stimulus                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                            | In a <i>non-return-to</i> format, output formatting allows the user to delay (skew) output signals relative to each other up to one full clock period. This aids in meeting or testing UUT setup and hold timing requirements.                                                                                                                                                                                                                                                                                                                                                  |

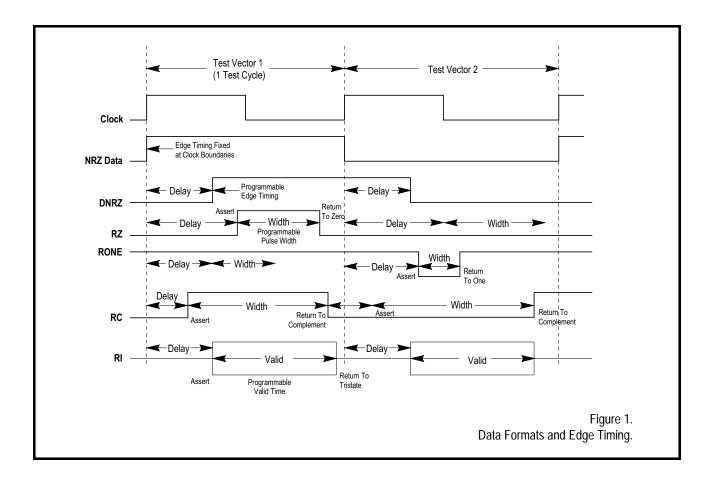

| Output Data Formatting     | Output formatting allows the user to manipulate stimulus output data by impressing a <i>return-to state</i> on the output, which is useful when generating high-speed clocks and strobes or serial data streams with a minimum amount of stimulus/response memory.                                                                                                                                                                                                                                                                                                              |

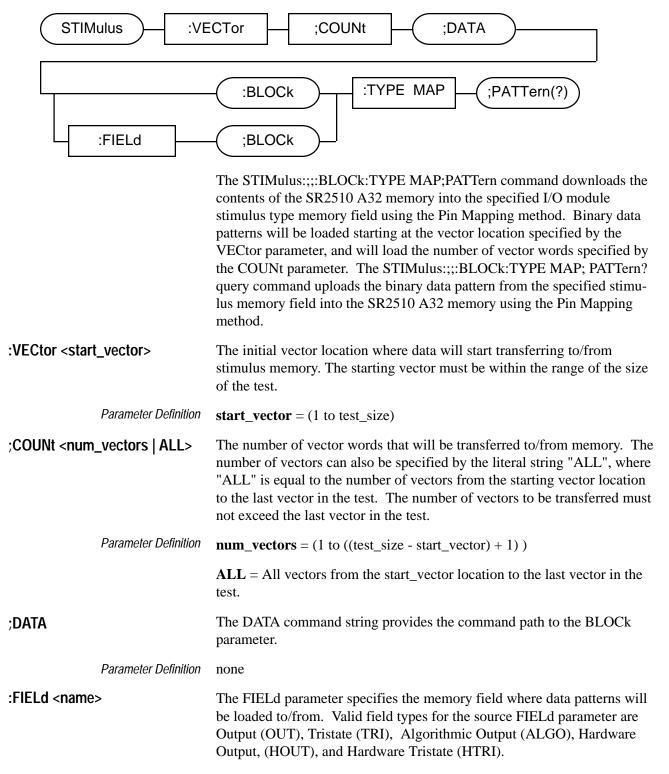

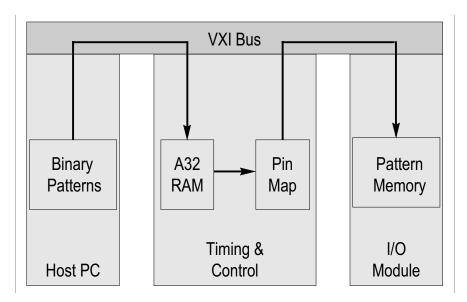

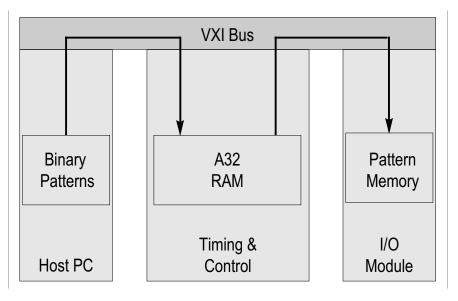

| VME A32 Dual Access Memory | The SR2510 module is configured with 1 MB of dual-access memory, which is mapped to VME A32 address space. This memory is a gateway used for high-speed binary data transfers of stimulus, response and/or record data to and from the SR2500 subsystem. The A32 memory may also be used for high-speed binary block transfers of complete test setups including control, stimulus and response data. The SR2510 module uses the <i>bus master</i> mode to transfer the data to or from any SR2520 expansion modules.                                                           |

| Data Rates                 | The SR2500 is capable of generating and recording data at rates ranging from 200 Hz to 25 MHz. Using an external clock input supplied to the front panel of the SR2510 module, the SR2500 can support data rates ranging from DC to 25 MHz. By default, the SR2500 is frequency-locked to an internal 10 MHz source. The SR2500 can also be locked to the VXI bus 10 MHz clock (CLK10) or an external 10 MHz reference, which is supplied to the front panel of the SR2510 module.                                                                                              |

|                            | <b>CRTSubroutine   RTSubroutine</b><br>This command initiates a conditional or unconditional return from a subroutine. Returns are not limited to 32 vector boundaries and may reside at any vector location. A <i>return</i> to an odd vector location requires (3) test cycles, while a <i>return</i> to an even vector requires (4) cycles.                                                                                                                                                                                                                                  |

|                            | This command allows the test to conditionally or unconditionally branch<br>to a subroutine vector location within a test. Subroutines must start on a<br>32 vector boundary. Test sequencing and pattern generation will continue<br>from that vector until a return instruction is encountered. After the return,<br>test sequencing and pattern generation continues from the vector immedi-<br>ately after the vector containing the subroutine branch. Subroutines may<br>be nested 8 levels deep and always require (4) test cycles to branch to the<br>subroutine vector. |

data is applied to the output pins, relative to the beginning of the test cycle. The width represents the duration of the output data before the data is returned to the defined *return-to* state. The delay time may be defined at any point within one system clock period. The width parameter must be a minimum of 10 ns and may not exceed one test cycle minus 10 ns. Data format widths may cross cycle boundaries, hence it is permissible to *assert* the state in one cycle, and to *hold* that state into the next cycle. When the internal clock system is used, the delay/width resolution is 12.5% of the system clock. NOTE: The system clock operates in the range of 12.5 MHz to 25.0 MHz. Hence, resolution will vary from 10 ns to 5 ns, respectively. The accuracy of the delay and width settings is 10 ns. When an external clock source is used, the resolution is one-half of the external clock period. The following formats are used to modify output data:

#### NRZ (Non-Return-to-Zero)

The default mode for output data formatting is NRZ. In this mode, no additional data formatting is impressed on the outputs. The output pins are driven to the defined state after the defined delay time, and remain in that state until the same time in the following cycle, at which point the pins are driven to the newly defined state. The width parameter is not used in NRZ format. True NRZ formatting would place the delay time at 0 ns. Because the NRZ delay time may be placed at any point within the clock cycle, NRZ may also be used for Delayed Non-Return-To-Zero (DNRZ) formats.

#### RZ (Return-to-Zero)

Return-to-Zero causes the output pins to be driven to the programmed state after the delay time and for the duration of width, and driven to "0" during the delay time and at the end of the width setting. If the tristate control for a pin indicates the pin should be tristated for the test cycle, the tristate control takes priority over the pin formatting and the pin will not be driven to the programmed state, nor return-to-zero.

#### RONE (Return-to-One)

The return-to-one mode causes the output pins to be driven to the programmed state after the delay time and for the duration of width, and driven to "1" during the delay time and at the end of the width setting. If the tristate control for a pin indicates the pin should be tristated for the test cycle, the tristate control takes priority over the pin formatting and the pin will not be driven to the programmed state, nor return-to-one.

#### RC (Return-to-Compliment)

The return-to-compliment mode causes the output to be driven to the programmed state after the delay time and driven to its compliment state

at the end of the width time. Prior to the assert time (during delay), the outputs are driven to the compliment of the programmed state for the previous cycle. If the tristate control for a pin indicates the pin should be tristated for the test cycle, the tristate control takes priority over the pin formatting and the pin will not be driven to the programmed state, nor return-to-complement.

#### RI (Return-to-Inhibit/Tristate)

The return-to-inhibit mode causes the output pins to be driven to the programmed state after the delay time and for the duration of width, and tristated during the delay time and at the end of the width setting. If the tristate control for a pin indicates the pin should be tristated for the test cycle, the tristate control takes priority over the pin formatting and the pin will be tristated for the entire test cycle.

### Input Data Formatting The SR2500 provides two methods of sampling and/or comparing the UUT response data:

#### Edge Mode

In edge mode, UUT response data is latched (sampled) into the input register at the defined time within the test cycle, and compared against the expected UUT response data, masking out any bits indicated by the mask ("don't care") memory. If a compare error is detected, the Error Latch is set. Depending on the record control settings, either the actual UUT response data or the results of the compare -- error data -- are stored in the record memory. Or, if the record control settings so indicate, no information is stored in the record memory.

In the real-time compare mode, the initial expected response comparison may be delayed a total of seven test cycles. This is to compensate for delays external to the SR2500.

#### Window Mode

The window mode is used to detect glitches. Whereas the edge mode samples the input pins (UUT response) at one instant in time, the window mode in effect samples the inputs over a period of time. The input data must match the expected state and must remain stable for the time duration defined. If the data does not match the expected response, or if the data transitions (glitches) at any time within the window, the result of the response comparison is false (assuming the respective bits are enabled for comparison). If the record memory is programmed to store errors, the bits with detected mismatches (glitches) are set high, even if the initial or final state of the input matches the expected value. Like the edge compare mode above, the initial expected response window comparison may be delayed a total of seven test cycles, again, to compensate for delays external to the SR2500.

#### Memory

The SR2500 uses several types of memory to perform specific functions. The SR2500 can be purchased in two sizes of stimulus/response/record memory, providing either 64K or 256K test vector depth.

#### **Control Memory**

The control memory provides the sequence instructions (program) for the control processor, which is responsible for the overall vector sequencing of the system. By default, a simple in-line test program of the same length as a defined test is automatically generated. Therefore, the default number of test vectors generated by the program is exactly equal to the length of the test program.

More complex programs may contain looping and conditional or unconditional branches, and may be used to generate many more test vectors than the defined length of the test program. These loop and branch instructions are typically combined with algorithmic pattern generation to produce the desired test vectors.

The stimulus and expected response memories are effectively addressed by the same address counter that drives the control program. Therefore, all stimulus and response fields, whether defined as algorithmic or nonalgorithmic, always sequence through the same number of vectors as the control processor. The record memory is addressed in an independent and linear sequence regardless of control program looping and branching.

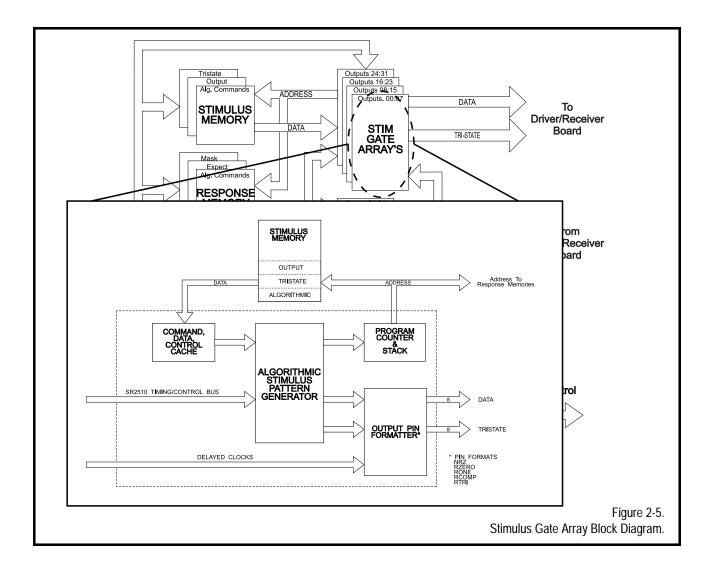

#### **Stimulus Memory**

The stimulus Memories control the generation of stimulus output data. The response memory is addressed by the control processor. For each stimulus pin, the following memory types are available:

**Output Memory**. The output memory defines the logic states that are driven to the UUT. In the non-algorithmic mode, this data is passed directly from RAM to the output pins, via the stimulus gate array. In the algorithmic mode, the data from the output memory is used as a literal value that may modify the current state of the output pin. One bit of the output memory is assigned for each bit in an output type field (OUT, OT, ALGO and HOUT).

**Tristate Memory**. Tristate memory determines if the output driver for a given output channel is enabled or disabled. One bit of this memory is assigned for each bit of the tristate type field (TRI, OT and HTRI). The

driver is enabled for the cycle if the corresponding tristate bit contains a value of "0". The driver is disabled (tristated) for the cycle if the corresponding tristate bit contains a value of "1".

**Stimulus Algorithmic Memory.** The stimulus algorithmic memory contains instructions that control the generation of algorithmic output data patterns. Four bits of this memory are used for each byte of algorithmic output type field (ALGO). These four bits determine which of the 16 possible algorithmic operations are to be carried out on that group of eight output bits. Non-algorithmic fields automatically set these bits to "0", which is the equivalent of the non-algorithmic command.

**Response Memory.** The response memories control the generation of the expected data patterns that are used in real-time compares. The results of the comparison may:

- Be returned at the end of the test

- Be used to control the test program sequence

- Be used to determine starting and stopping of record memory

- Be used to determine starting and stopping of CRC sampling

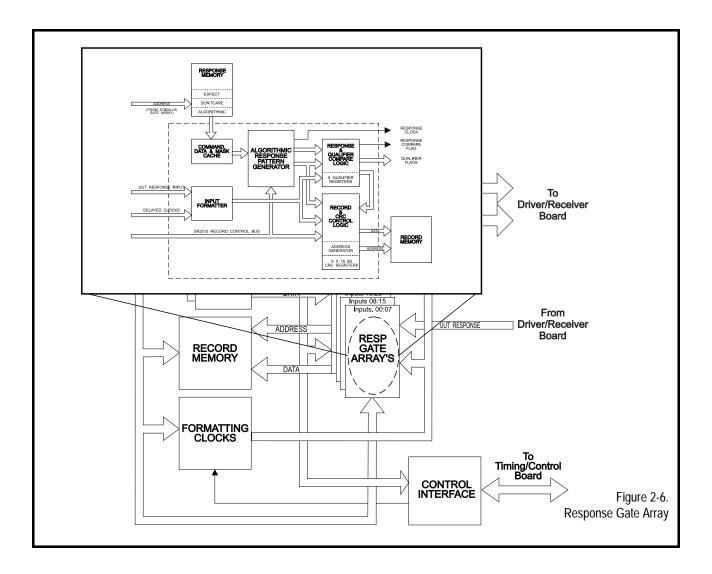

The response memory is addressed by the control processor. For each input pin, the following response memories are available:

#### **Expect Memory**

The expect memory defines the logic state expected to be returned from the UUT. In the non-algorithmic mode, the data in RAM is directly used for the comparison operation. In the algorithmic mode, the data from the expect memory is used as a literal value that may modify the current expected state. One bit of this memory is assigned for each bit in an expect type field (EXP, ED, ALGE and HEXP).

#### Don't Care Memory

The "don't care" (mask) memory, determines if the UUT response for a given input channel is compared against the expected state of that channel for the current test vector. One bit of this memory is assigned for each bit in a "don't care" type field (DON, ED, HDON). The input value is compared to the expected value if the corresponding bit in the "don't care" memory is programmed with a value of 0. The result of the compare is ignored (masked) if the corresponding "don't care" bit is programmed with a value of 1. When the record error data criteria is selected, a value of 0 is stored to record memory for each bit where the corresponding bit in the "don't care" memory is set to 1.

The "don't care" memory is also used as a mask for enabling signature analysis checksum (CRC) calculations on the individual input pins.

#### Response Algorithmic Memory

|                                                 | The response algorithmic memory contains instructions that control the generation of algorithmic expected data patterns. Four bits of this memory are used for each byte of expected response type field. These four bits determine which of the 16 possible algorithmic operations are to be carried out on that group of eight expect bits. Non-algorithmic fields automatically set these bits to "0", which is the equivalent of the non-algorithmic command.                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Record Memory                                   | The record memory's function is like that of a logic analyzer, i.e., record-<br>ing data. While the record memory is bundled under the same command<br>subsystem as the response memories, it functions as a wholly separate<br>subsystem from stimulus and response. For this reason it has not been<br>included under the response subsystem in this technical description.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                 | The user may elect to store to record memory in one of two ways either<br>the data values returned by the UUT, or the result of a bit-wise comparison<br>between the data from the UUT and the expected data generated by the<br>expect/"don't care" memories (errors). This function is selected with the<br>filter parameter in the Record:Trace command subsystem. In the store<br>error data mode, a value of "1" is stored for each input bit that does not<br>match the expected value. If the input field is operating in the window<br>mode, a value of "1" is stored for each bit in which a pattern mismatch<br>occurs or for each bit where a mismatch or a glitch was detected. If the<br>"don't care" bit is set to "1", a value of "0" is stored regardless of whether<br>a compare mismatch or a glitch occurs. |

|                                                 | Record memory may only be loaded as a result of recording UUT re-<br>sponses. It may be queried by the user or used to copy recorded results to<br>expected memory (response learning), but may not be directly loaded by<br>the user.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                 | Unlike the stimulus and response memories, the record memory is ad-<br>dressed and controlled independently of the control processor. The user<br>may selectively store or not store, based on the evaluation of preset trigger<br>conditions and qualifiers. The record operations, as well as the sampling<br>of the CRC (signature analysis) registers, are independently controlled by<br>a 16 level record state machine. This state machine allows for simple or<br>complex triggering capabilities similar to those found in a conventional<br>logic analyzer.                                                                                                                                                                                                                                                          |

| Record Memory and Signature<br>Analysis Control | The SR2500 can perform hardware real-time signature analysis on the data stream of all input pins during qualified cycles. Signature analysis is performed by calculating a 16 bit Cyclic Redundancy Check (CRC) value for each input pin. The results of the CRC calculation are stored in a 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

bit CRC register, one register for each input pin. CRC calculations are performed when enabled by the record control state machine and when the corresponding "don't care" bit is set to "0". The CCITT standard communication polynomial is used to perform the CRC calculations and the CRC value is the 16 bit remainder produced by dividing the input stream by the following polynomial, using Galois field arithmetic:

$Gx = 1 + x^5 + x^{12}$

Program LanguagesThe SR2500 programming commands are based on the Standard Commands for Programmable Instruments (SCPI) syntax and are used to set up and query all system functions and execute all run-time controls.For complete programming instructions, refer to Chapter 3, "Programming."

#### CHAPTER 3

## Programming

SCPI Command Syntax

The SR2500 is controlled via a set of word serial commands patterned after the 1993 edition of the Standard Commands for Programmable Instruments (SCPI). To accommodate the robust feature set of the SR2500, many additional commands have been added. Although these additional commands are not defined in SCPI, they do follow the rules and syntax of SCPI commands and provide access to the SR2500's unique features.

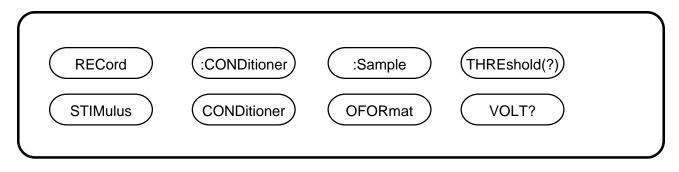

SCPI commands are defined in a tree structure starting with a basic command function, called the command root. The tree's functionality is expanded by adding command decriptors, known as command branches. The final command parameter is called a command leaf. With this structure, commands may be logically grouped together based on functionality. Commands defined by SCPI are denoted by the word "SCPI". The commands that follow the SCPI syntax but are not defined by SCPI are denoted by the word "NON-SCPI."

SCPI branches and leaf commands use the colon (:) character as a prefix, denoting descent into the command tree by one level. Root commands have no prefix. Some SCPI command paths are quite lengthy, and to avoid typing in the full command path, several short-cuts are available. For example, some SCPI command words are optional. These commands are listed in brackets []. Also, each SCPI command has a long and an abbreviated format. The required abbreviated format is shown in capital letters, while the characters making up the optional long format are shown in lowercase. The following two command strings are identical in functionality:

STIMULUS:CMACRO:LABEL:VECTOR 10;REDEFINE START STIM:LAB:VEC 10;RED START

Another shortcut is the semi-colon character (;). Using a semi-colon allows the user to remain at the same level in the command path and enter multiple parameter values, rather than having to re-enter the entire command path for each value entered. In the following example, the first two commands may be replaced by the third example:

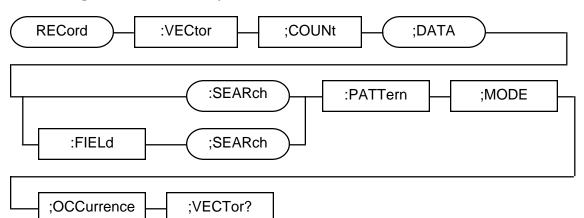

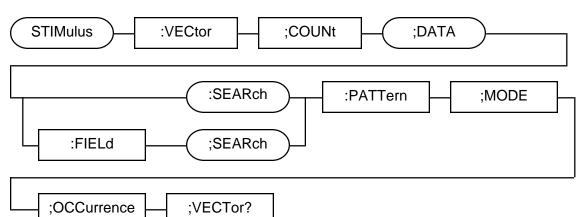

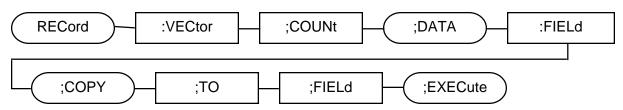

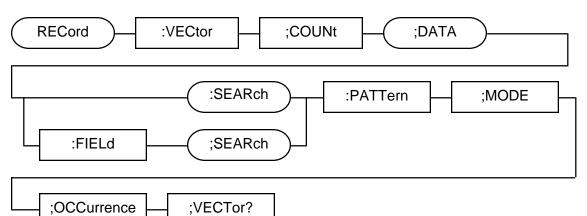

RECORD: VECTOR 1;COUNT ALL;DATA:FIELD D16\_09;CLEAR RECORD: VECTOR 1;COUNT ALL;DATA:FIELD D08\_0;CLEAR RECORD: VECTOR 1;COUNT ALL;DATA:FIELD D16\_09;CLEAR;FIELD D08\_0;CLEAR

| command               | Command words take three forms, ROOT, BRANCH, and LEAF. The<br>ROOT is the beginning of a command, i.e. the first word in a com-<br>mand string. Branches are the connecting paths between the ROOT<br>and the LEAF. Branches may or may not have parameters associated<br>with them, or may have a suffix, usually a channel indicator. The<br>LEAF terminates the command string and may or may not have<br>parameters associated with it. |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| command               | Indicates commands which do not have parameters.                                                                                                                                                                                                                                                                                                                                                                                             |

| command               | Indicates commands with parameters.                                                                                                                                                                                                                                                                                                                                                                                                          |

| command(?)            | Commands that are followed by a question mark in parenthesis indicate a command format supporting both a command and a command query.                                                                                                                                                                                                                                                                                                        |

| command?              | Command strings followed by a question mark without parenthesis indicates a command query only.                                                                                                                                                                                                                                                                                                                                              |

| UPPERCASE             | Command characters displayed in uppercase are required characters.                                                                                                                                                                                                                                                                                                                                                                           |

| lowercase             | Command characters displayed in lowercase are optional characters.                                                                                                                                                                                                                                                                                                                                                                           |